Устройство для передачи асинхронных импульсных сигналов

Иллюстрации

Показать всеРеферат

Мюз Советских

Социалистических

Республик

ОП ИС

46095 .

ИЗОБРЕТЕН

К АВТОРСКОМУ СВИДИТИПЬСТ (61) Зависимое от авт. свидетельства (22) Заявлено 28.08.72 (21) 1823883/2

М. Кл. QO8c 19/28 с присоединением .заявки №вЂ” (32) Приоритет

Опубликовано 05.:10.74, Бюллетень

Государстввиный комитат

Соввта Министров СССР во делам изобретениЯ и открытий

УДК 621.398:654.. 93(088.8) Дата опубликования описания 24.04.7 (72) Авторы изобретения О. Н. Андреев, И А. Померанцев, А. С. Герасимов, Г. И. Гладков, Ю. Г. Балахнин и И. М. Амелин (7I) Заявитель (54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ АСИНХРОННЫХ

ИМПУЛЬСНЫХ СИГНАЛОВ

Изобретение относится к технике передачи импульсных сигналов, Устройство может быть использовано в автоматизированных системах управления при организации каналов съема дискретной информации.

Известно устройство для передачи асинхронных импульсных сигналов, содержашее датчик импульсов, триггер буферной памяти, каналы передачи и управления, две схемы

"И".

Бель изобретения - повышение достовер ности передачи сигналов — достигается тем что в предлагаемом устройстве выход датчика импульсов дополнительно подключен к соответствуюшим входам обеих схем "И через последовательно соединенные схему

"ИЛИ", управлявмую с противофазного выхода триггера буферной памяти, и дополнительный триггер, управляемый по единичнсо му входу сигналами "подготовка считыва ния".

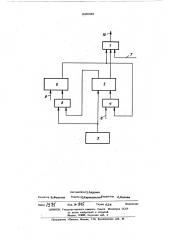

На чертеже представлена функциональная схема устройства.

К одному из входов схемы "И" подклю.чен через триггер буферной памяти 2 датчик асинхронных импульсов 3, Схема И 4 подклкнена к нулевому входу триггера 2.

Датчик 3 через схему "ИЛИ" 5 и дополнительный триггер 6 подключен к другим входам обеих схем И". По второму входу схема "ИЛИ" 5 управляется потенциалом с нулевого выхода триггера 2. Таким обра» .зом, будучи в исходном состоянии, триггер

2 жестко фиксирует нулевое состояние щ триггера 6. Бепи упоавляюших сигналов

"Считывание" 7 и «Сброс i 8 подключены к соответствуюшим входам схем "И", цепь сигнала "Подготовка считывания" 9 - к единичному входу триггера 6. Сигнал со

15 схемы считывания "И" 1 поступаем в канал передачи информации 10.

В процессе работы с датчика 3 на схе му устройства асинхронно поступают импузнсы записи с известным минимальным у} периодом следования. При отсутствйи сигнала "Запись", а также в момент его действия на триггер 2 сигнал "Подготовка считывания" 9 не может перевести.дополни . тельный триггер 6 в единичное состояние, х5 так как последний через сборку "ИЛИ " 5

446095

3 фиксируется в исходном состоянии или потенциалом с противофазного выхода триггера 2 или импульсом с датчика 3, Поэтому, если управляющий сигнал Подготовка считывания заканчивается раньше сигнала Запись" с датчика, последующие управ ляющие сигналы — "Считывание" 7 и Сброс".

8 вследствие запрещающего воздействия потенциала с единичного выхода триггера

6 не выполняют своих функций. В следующем такте поступления управляющих им» пульсов, когда в триггере 2 уже зафиксирована "единица информации, импульс "Запи ь" закончился и через схему ИЛИ" 5 запрещающее действие сигнала с триггера

2 на триггер 6 отсутствует, сигнал "Подготовка считывания переводит дополнительный триггер 6 в "единичное" состояние.

По сигналу "Считывание" 9 срабатывает схема "И 1, подготовленная разрешающими потенциалами с единичных выходов триггеров 2 и 6, и по каналу связи 10 передается информационный сигнал.

Следующий за импульсом "Считывание"

9 управляющий сигнал "Сброс" 8 через схему "И" 4, подготовленную разрешающим потенциалом с единичного выхода триггера

6, переводит триггер 2 в нулевое состояние, Потенциал с нулевого выхода триггера 2, действуя через схему "И.ЦИ" 5 на дополнительный триггер 6, вновь фиксирует его исходное состояние до очередной записи информации в буферную память устройст ва.

В данной схеме даже в момент совпаде

5 ния задних фронтов сигналов "Запись" и

Подготовка считывания4 исключена вероят ,ность двойного счйтывайия или потери ин формации.

Предмет изобретения

Устройство для передачи асинхронных щ импульсных сигналов, содержащее на входе канала связи схему "И, управляемую, сигналами считывания, к одному из входов, которой подключен датчик импульсов через триггер буферной памяти, к нулевому вхоф ду которого, в свою очередь, подключена вспомогательная схема "И", управляемая сигналами сброса, о т л и ч а ю ш е е с я тем, что, с целью повышения достоверно» сти передачи сигналов, выход датчика

25 импульсов дополнительно подключен к соответствующим входам обеих схем И» через последовательно соединенные схему

"ИЛИ", управляемую с противофазного выхода триггера буферной памяти, и до30 полнительный триггер, управляемый по единичному входу сигналами "Подготовка считывания".

Составитель С,фурора

Редактор 5.Федотов Техред H. арандашовФорректор Л отои„н цаааа /3Q паа. рр отК тираж пр4 поаоасаоа

ЦНИИПИ Государственного комитета Совета Министров СССР но делам изобретений и открытий

Москва, !)3035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская .наб., 24