Ячейка памяти

Иллюстрации

Показать всеРеферат

тен;-:,:.-,: б и бл к о т,-- „,;:, ; .—,. л

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистимеских

Республик (») 446È1 уК *» (61) Зависимое от авт. свидетельства— (22) Заявлено 30 ° 03. 72 (21/ 697 8-24 (51) М. Кл.

$ 11c 11/34 с присоединением заявки

Государственный номитет

Совета Министров СССР оо делам изобретений и OTKpblTHH (32) Приоритет

Опубликовано05. 10.74Бюллетень No 37

Дата опубликования описания l5.I2 ° 74 (5з) Удк 687.327. .066(088. 81 (72) Автор изобретения

Н.А. Чубарев (71) Заявитель (54) ЯЧЕЙКА ПАМЯТИ

4

Предлагаемая ячейка памяти отно- сится к области автоматических устройств и, в частности, может быть, применена для одновременного пост рое11ия двух видов запоминающих ус- 5 тройств постоянного на трансформаторах ячеек (ПЗУ) и оперативного на тиристорах тех же ячеек (ОЗУ). Число разрядов каждого вида ЗУ равно числу используемых ячеек. 1О

В известных автоматических устойствах считанная инФормация с

ПЗУ) переносится в (ОЗУ), собранные, обычно, на триггерах с выходнымй усилителями после каждого триг-15 гера. Функции триггера и выходного усилителя в ОЗУ может выполнять ячейка памяти на тиристоре. Схемы таких ОЗУ значительно проще.

Однако известные ячейки памяти 20 на тиристорах имеют низкую помехоустойчивость из-за большого выброса входных 11арВМВТрОВ тиристоров.

Целью изооретония является повышение помехоустойчивссти ячейки па- 25

2 мяти на тиристоре.

В предлагаемой ячейке памяти эта цель достигается тем,что она содержит стабистор, включенный между катодом тиристора и шиной питания, стабилитрон, анод которого подключен к аноду диода, а катод — к четвертому Резистору, и резистор, под1 ключенныи к точке соединения анода диода и анода стабилитрона и к 1цине питания.

Помехоустойчивость ячейки повышается благодаря пороговым напряжениям, возникаю1цим на стабисторе и стабйлитроне при прохождении импульсного сигнала в цепи управления тиристора.

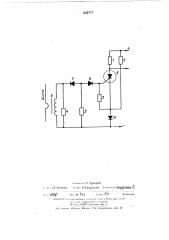

Схема ячейки памяти представлена на чертеже.

Ячейка содержит резисторы I-5; трансформатор 6, стабилитрон 7,дйод

8, тиристор 9 и стабистор I0.

Резистор E обеспечивает минимальный ток, необходимый для поддержания тиристора во включенном состоя446133

3 нии. Резистор 5 и диод 8 предохраняют управляющий электрод тиристора от импульсов отрицательной полярности.

Резисторы 2 и 5 обеспечивают неооходимые режимы работы стабистора

I0 и стабилитрона 7.

Резистор Ф уменьшает входное сопротивление ячейки для малых сигналов и помех

Через сердечник трансформатора 6 10 проводятся шины ПЗУ, построенного на ячейках. размер трансформатора определяется проходящих через него шин и зависит от числа слов ПЗУ.

Конструктивно ячейка выполнена в виде модуля с печатным монтажом.

Ячейка памяти работает следующим образом.

При пропускании импульса тока считывания по шине, образующей первичную обмотку трайсформатора B один виток, на его вторичной обмотке появляется импульс, который через стабилитрон 7 и дйод 8 поступает на управляющий электрод тиристора 9. Тиристор срабатывает и оста-. ется во включенном состоянии по окончании импульса. Таким образом, производится передача информации йз

ПЗУ, построенного на трансформато- зо рах ячеек, в ОЗУ построенное на тиристорах тех же ячеек.

Помехи, появляющиеся на шинах

ПЗУ, не вызывают срабатывания тиристора ячейки, так как их величина недостаточна для преодоления напряжения стабилизации стабилитрона 7 и стабистора l0.

Сброс информации (выключение тиристора) может осуществляться путем подачи отрицательного импульса на анод тиристора или путем замыкания анода тиристора с шиной питания.

ПРЕДМЕТ ИЗОБРЕТЕНИЯ

Ячейка памяти, содержащая тиристор, анод и катод которого через первый и второй резисторы подключены к одной из шин питания, управляющий электрод тиристора подключен к катоду диода и через третий резистор к катоду тиристора, трансформа,тор, параллельно вторичной обмотке которого включен четвертый резистор,отличающаяся тем что,с целью повйшения помехоустойчивости и надежности работы ячейки, она содержит стабистор,включеныйй между катодом тиристора и другой шиной питания,стабитрон, анод которого подключен к аноду дйода, а катод — к четвертому резистору, и пятый резистор, подключенный к "î÷êå соединения анода диода и анода стабилитрона и к другой шине питания.! и:! !а! а 11.Ч ЬДРЕВ ! ":Р » 31.ЧаВ ШЬЯН К РРс I КаРУШИНа C. «.!,! Л;1(екина

>и I ира к

Юб

Г!о!!писиое

ill! !! рии!и! «!Ь!!.и!», Москва, Г 59, Берсжкоиская иаб., 24

Ill llllll ill I iii ) Idl ñ(!!еиио! и л! яи !с!а (>!Sd! d Миии.!р!>в (.ОР ио а .!dt! и !Оорс1сии(! и !)1!.!>л!!и!!

М слил, 1!3035, !!ауи!скак наб, 4