Умножитель частоты

Иллюстрации

Показать всеРеферат

/. изто

О fl И C А"-Н И-Е.

ИЗОБРЕТЕН ИЯ

Союз Советскин

Соцмалмстическмх

Ресаублнк

/ (11), 446940

К АВТОРСКОМУ СВИДБТИЛвеСТОУ (Gl) Зависимое от авт. свидетельства— (22) Заявлено 06. 03. 73 (21) I890433/26-9 (51) М Кл.

Н 036 9/r0

& 06 7/I 6 с присоединением заявки—

Госудерстеенный комнтет

Совете Мнннстрое СССР по денем нзобретеннй н открытей (32) Приоритет—

Опубликовано 15. IQ. 7 бюллетень № 38 (45)! Дата опубликования описания15. I2. 7 (53) У Д l(62 г;-",7 1,:,:1

{088. ;1

В.M. Трохин, M,II. Четаев, H.È.Ýíòèíà,À.M.Бродецкий и

13.И.Пенкина (72) Авторы изобретения (7 I) Заявитель

Украинский заочный политехнический институт

{54) УМНОЖИТЕЛЬ ЧАСТОТИ

Изобретение относится к техническим средствам вычислительной техники, в частности к широкодиапазонным умножителям частоты, и может быть использовано в вычислительных устройствах, в системах автоматического уйравления, телемеханики и других устройствах, имеющих частотный выход.

Известен умножитель частоты, содержащий управляемый генератор, делитель частоты в цепи обратной связи и триггер.

Однако в известном умножителе работа диапазона умножаемых частот (полосы синхронизма и захвата) незначительна.

С целью расширения полосы захвата синхронизации и защиты схемы умножителя от потерь импульсов умножаемой частоты в предлагаемый умножитель частоты введены генератор тактовых импульсов, четыре схемы синхронизации, два триггерных счетчика, схема защиты и ба(лансный демодулятор, при этом вы2 ход генер а тор а тактовых импульсов подключен непосредственно к одним входам триггерных счетчиков и через две схемы синхронизации — но

5 вторым входам этих же триггерпых счетчиков, выходы которых через две другие схемы синхронизацйи соединены со входами схемы защ1.ill, выход последней через последолзи тельно соединенные триггер и балансный демодулятор подключен ко входу управляемого генератора.

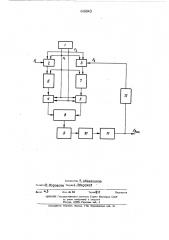

На чертеже изображена функциональная схема предлагаемого множителя частоты.

Предлагаемйй умножитель содержит генератор I тактовых импу с-.,, четыре схемы синхронизации 2-5, два триггерных счетчика 6 и 7, схему защиты 8 триггер 9, балансныЫ

2î МОдуЛятОр Ые уПраВЛяЕМЫй ГЕНЕратср

П, делитель частоты 12.

Принцип работы умножителя час-. тоты целесообразно рассматривать в трех режимах.

В первом режиме при отсутствии ! импульсов умножаемой частоты /, и

446940

3 импульсов частоты, f, ооратной связи схема работает следующим образом.

Генератор I тактовых импульсов периодически вырабатывает однопо- 5 лярные импульсы тактовых частот

F, и F,, смещенных во времени на половину периода их колебаний.

Импульсы тактовой частоты F; поступая на счетные входы младших разрядов триггерных счетчиков 6 и

7, выполняющих роль интегрирующего устройства, синхронно заполняют их. Благодаря начальной записи единицы в один из старших разрядов триггерных счетчиков выходные импульсы со старших разрядов счетчиков сдвигаются во времени точно на половину их периода. 20

Воздействуя через схему защиты

8 на триггер 9, преобразующий совместно с триггерными счетчиками 6 и 7 импульсы входной частоты 7; и частоты /, обратной связи в широтно-импульсное напряжение, среднее значение которого пропорционально интегралу по времени от разности частот f, и f<, эти импульсы вызывают колебательный режим триггера со скважностью, равной D,5, при этом напряженйе на выходе балансного демодулятора IQ отсутствует, так как он выполнен по балансной схеме и представляет собой активный R С-фильтр нижних зб частот с усилителем.

Во втором режиме работа схемы при наличии импульсов умножаемой частоты, происходит следующим образом.

Импульсы частоты f поступают на вход схемы синхронизации 2, которая запоминает их путем изменения состоянкя триггера, входящего в эту схему, и осуществляет ввод 45 импульсов частоты f, на второй счетный вход триггерного счетчика

6 синхронно с импульсом тактовой частоты Fi . Аналогично раоотают схемы синхронизации 3, 4- и 5, в 5о результате чего достигается защита схемы умножителя от сбоев и беэвозвратнои потери информации.

Помимо тактовых импульсов частоты б триггерные счетчики 6 и ы

7 заполняются импульсами частот и, это приводит к изменению скважности импульсного напряжения триггера 9, что, в свою очередь, вызывает йоявление среднего значения постоянного напряжения на выходе балансного демодулятора I0.

На выходе управляемого генератора П появляется импульсное напряжение, частота которого соответствует коэффициенту деления, установленному на делителе частоты I2.

Следовательно, в установившемся режиме строго выдерживается равенство f,. = f, В третьем режиме цроцессв.работы умножителя частоты может произойти скачкообразное изменение значения умножаемой частоты при этом наступает сбой, безвозвратная потеря некоторого количества импульсов умножаемой частоты и нарушение синхронизма; для избежания этого в умножителе предусмотрена схема защиты 8, представляющая собой реверсивйый управляемый сдвиговый регистр, который совместно с триггерными счетчиками 6 и 7 обеспечивает бесперебойную работу умножителя в динамических режимах.

При резком возрастании частоты

f, (однако при условии f, с Fi ) частота выходных импульсов со старшего разряда триггерного счетчика

6 может превысить частоту выходных импульсов со старшего разряда триггерного счетчика 7 в два и более раза. В этом случае реверсивный сдвиговый регистр схемы защиты

8 прекращает колебательный режим триггера 9, установив его в состояние, при котором полное напряжение йоступает на управляемый генератор, а последний, вырабатывая сигнал более высокой частоты, осуществляет компенсацию рассогласования в схеме. Одновременно схема защиты запоминает количество импульсов рассогласования и разре-, шает нормальный режим раооты выходного триггера только при условии полнои компенсации.

При таком способе защиты схемы умножителя несколько ухудшаются динамические показатели, но отсутствует потеря синхронизйа и безвозвратная потеря импульсов умножаемой частоты

Емкость динайической памяти схемы защиты определяется формулой

Я 2 "(е -2) гдв и — количество разрядов триггерного счетчика;

m — количество разрядов реверсивного регистра.

Возвращение схемы в нормальный режим работы происходит автоматически по мере уменьшения разности

5 между количеством импульсов частоты /, и количеством импульсов частоты f>

Благодаря частотно-фазовому принципу работы цифро-аналогового интегратора, свойствам дискретного делителя частоты и построению умножителя с обратной связью статическая точность умножителя может достигать 0,0I$ и выше.

При выборе соответствующих элементов тактовые частоты могут быть порядка мегагерц, а постоянная времени активного RС-фильтра

- порядка нескольких микросекунд, что обеспечивает сравнительно высокую динамическую точность умножителя.

Умножитель частоты представляет собой цифровую астатическую следящую систему частотно-фазового типа, а так как в нем триггерные счетчики б и 7 выполняют роль интеграторов и, кроме того, имеется динамическая память на регистре 8 то при умножении низких частот в паузах между импульсами входного сигнала цепь обратной связи не размыкается.

Благодаря этому в умножителе полоса синхронизма совпадает с полосой захвата, которые, в свою очередь, определяются свойствами применяемого перестраиваемого по частоте генератора. Например, при использовании в качестве управляемого генератора устройства типа широкодиапазонного мультивибратора с коэффициентом перекрытия по

446940 частоте йорядка IQ при частоте входного сигнала 0,I + 10 0 Гц (перекрытие по частоте I0 ) диапазон захвата и синхронизма совпадает с диапазоном изменения частоты сигнала, следовательно, предлагаемый умножитель частоты может быть эффективно использован при умножении низких и инфранизких частот со значительными {порядка IQ и более) коэффициентами умножения.

ПРЕДМЕТ ИЬОБРЕТЕНИЯ

Умножитель частоты, содержа щий управляемый генератор, делитель частоты в цепи обратйой связи и триггер, о т л и ч а ю щ и йс я тем, что, с целью расширения полосы захвата синхронизации и защиты схемы умножителя от потерь импульсов умножаемой частоты, в него введены генератор тактовых импульсов, четыре схемы синхронизации, два триггерных счетчика, схема защиты и балансный демодулятор, при этом выход генератора тактовых импульсов подключен непосредственно к одним входам триггерных счетчиков и через две схезо мы синхронизации- - к вторым входам этих же триггерных счетчиков, выходы которых через две другие схемы синхронизации соединены с входами схемы защиты, выход последней через последовательно соединенные триггер и балансный демодулятор подключен к входу управляемого генератора.

446940

Составитель T. Afeaapzeaa

РедактоЯ . fPpppppZa ТехредА. ЗбЯРСКИЙ

Заказ 4(З

Изд. М О6 ТиражЩ) Подписное

Предприятие «Патент», Москва, Г-б9, Бережковская наб., 24

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4