Устройство запаздывания

Иллюстрации

Показать всеРеферат

1 з

ОП ИСАНЙЕ

ИЗОБРЕТЕН ЙЯ

К АВТОРСКОМУ СВИДЙНЛЬСТВУ (! 1), 446942

Союз Советских

Социалистимеских

Республик (61) Зависимое от авт. свидетельства— (22) Заявлено 27е06 ° 72 (21)I802I63/?824 (51) М Кл, н озй, vpo

Ь Овец 7/02 (53) УДК

68I 327 (088,8) с присоединением заявки—

Государственный комитет

Совета Министров СССР оо делам изобретений и открытий (32) Приоритет

Опубликованоз.5ЛО®74Бюллетень № 38 (45),Дата опубликования описания25 IP,7ф (72) Автор,. изобретения

А С Воробьев (71) Заявитель

Ордена Ленина институт проблем управления (автоматики и телемеханики) (>Ф) УСТРОЙСТВО ЗАПАЗДЫВАНИЯ

Изобретение относится к об- I ласти аналоговой вычислительной техники и может быть использовано при моделировании на универсальных АВМ систем, содержащих звенья временного запаздывания (в том числе и управляемого), а также при построении блоков запаздывания.

Известны устройства, имитирующие запаздывание путем воспроизведения с помощью четырех операционных усилителей первых трех членов разложения требуемой передаточной функции в ряд Паде. При этом часть передаточной функции звена запаздывания, предполагающая наличие дифференцирования, воспроизводится с помощью разйости двух передаточных функций что позволяет избежать явлого ли фереицирования.

Известны устройства указанного типа, обеспечивающие воспроизведение регулируемого запаздывания.

Однако в существующих устрой ствах вследствие использования раэ2 (ности двух передаточных функций для достижения необходимой точности требуется строгий баланс ря- . да элементов схемы, нарушение коб торого приводит к существенным искажениям не только ф азовой, но и амплитудной частотных характеристик устройства в определенных диапазонах частоты и амплитуды входно1о го сигнала. Эти показания усугубляются в схемах с управляемым запаздыванием.

Целью изобретения является повышение точности и имитации эапаэ15 дывания за счет перестройки схемы воспроизведения известной передаточной функции.

Указанная цель .достигается непосредственным воспроизведением части передаточной ункции звена запаздывания путем соединения выхода апериодического звена с одним из входов сумматора. При этом в отличие от известных схем отсутствуют непосредственные связи входа устройства со входом интвгрирующе446942

Тр

W() =-К 1- „, 12 2 е К вЂ” методическая ошибка; д у р единена со входом сумматора 2 и со входом апериодического звена 3.

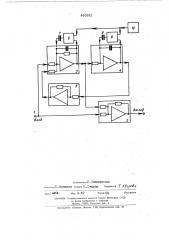

Во внешнюю обратную связь апериодического звена между его выходом гд - время запаздывания, обеспечивает воспроизведение на его выходе сигнала с запаздыванием на величину 7 относительно входа с известной методической ошибкой. Величи-ны постоянных времени апериодичеси одним входом включены последовательно соединенные интегратор Ф и инвертор 5. Все указанные звенья (апериодическое, интегрирующее, инвертор и сумматор) собраны по известным схемам на операционных усилителях постоянного тока, обладающих свойством инвертирования знака. Выход апериодического звена соединен непосредственно со вторым входом сумматора 2. В цепь обратной связи апериодического звена включена дополнительная параллельная ветвь, состоящая из последовательно соединенного множительного знака 6 и конденсатора 7; аналогичная ветвь, состоящая йз множительного звейа 8 и конденсатора 9 используется в цепи обратной связи интегратора. Вторые входы множительных звейьев соединены с источником I0 управляющего сигнала.

Передаточная функция устройства при отключенном входе сумматора и постоянном управляющем сигнале имеет вид:

;кого звена и интегратора, а следовательно, и величина запаздывания

Т, являются линейными функциями управляющего сигнала, поступающего с источника IO на соответствующие входы множительных звеньев б и 8.

ПРЕДМЕТ ИЗОБРЕТЕНИЯ

Устройство запаздывания, содержащее сумматор и апериодйческое звено, входы которых соединены с входной клеммой устройства, в обратную цепь апериодического звена включены последовательно соединенные интегрирующее звено и инвертор, блок управления, состоящий из множительных звеньев, включенных в обратную цепь апериодическо35 у 4 )

<И а р+ р+а„ где Ы вЂ” постоянные коэффициенты, p — оператор дифференцирования.

Для реализации ее не пот ебовалось ни непосредственного ди ференцирования, ни вычитания одно переro звена и интегратора, а управляющие входи соединены с источником

45 управляющего сигнала, о т л и ч аю щ е е с я тем, что, с целью повышения точности работы устройства, выход апериодического звена подключен ко входу сумматора. го звена и выхода последнего со вхо- даточной функции из другой, что дом сумматора. Помимо повышения точ- обеспечивает в реальных условиях ности воспроизведения запаздывания более точнов выполнение определяезто несколько упрощает схему уст- мых ею преобразований сигнала по ройства, уменьшает число и упрощает 5 сравнению с известными устройствами. некоторйе из уравнений, связываю- При соответствующим образом выбранщих между собой ее параметры. ных параметрах схемы общая передаНа чертеже показана блок-схема точная функция нредлагаемог0 устустройства. ройства

Вхо ная клемма I ст ойства со- 1о

4 46942

3»<» 62

Изд. М 30

Тираж Щ Подписное

Ц11ИИ1 1И Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская иаб., 4!!редариятие «Патент», Москва, Г-59, Бережковская наб., 24

Составитель Л а СНИЬШ4ИК OBB е - ° рБ.Панкина т реа Н.Сенина Kopp -ap Т Хаоаеаа