Устройство для выбора среднего по величине двоичного числа

Иллюстрации

Показать всеРеферат

(72) Авторы изобретения В. И. Спиридонов, В. И. денисов, H. В. Кириченко, Е. В. Кислинский и В. П. Супрун (71) Заявитель (з4) устройство для вывогл середнего по величине

ДВОИЧНОГО; ЧИСЛА

Изобретение относится к области автоматики и вычислительной техники и может найти применение в резервированных цифровых системах автоматического управления.

Известно устройство для выбора достоверной информации из синхронно поступающих на обработку двоичных кодов, содержащее мажоритарный элемент, триггеры выдачи единиц и триггеры выдачи нулей, управляемые схемами "И анализа единиц и схемами "И" анализа нулей.

Недостатком известного устройства является невозможность обработки несинхронной информации и аппаратурная избыточность при подключении его к синхронизи рующему устройству.

Целью изобретении является упрощение схемы и расширение функциональных возможн остей.

Для этого в предложенном устройстве единичные и нулевые выходы входных три| геров соединены со вторыми входами соот ветствующих схем "И" анализа единиц и .нулей, нулевые входы — с единичными выходами триггеров выдачи нулей, а единичные входы — с единичными выходами триг. геров выдачи. единиц, причем третьи входы схем "И анализа йулей и единиц подключены к шине синхронизации.

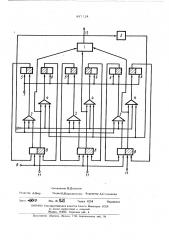

Эта позволяет получать достоверную информацию из несинхронно поступающих двоичных кодов, На чертеже представлена функциональная схема описываемого устройства.

Схема содержит мажоритарный элемент

1, - схему "И" анализа нулей 2„ инвертор 3, схему "И" анализа единиц 4, триг геры выдачи нулей 5, триггеры выдачи

1 единиц 6, шину 7 начальной установки, входные триггеры 8, шину подготовки приема информации 9, шину синхронизации 10, входные шины 11 и выход 12.

Устройство работает следующим обрая зом.

На входы 11 поступают сигналы от каналов резервированного устройства последовательным двоичным кодом, начиная со старших разрядов. Для определенности буя дем считать, что единице в разряде кода

447714 соотвевствует высокий потенциал, а нулю— низкий. В- исходном состоянии после подачи сигнала по шинам 7 и 9 нулевые выходы триггеров 5, 6 и 8 имеют высокий .потенциал, а единичные — низкий. Асинхронно принятая информация запоминается на триггерах 8, с которых поступает иа межоритный элемент 1 и схемы "И" 2 и ,4. Через время, определяемое максималь;ной рассинхронизацией каналов и включе«шем триггеров 8, по шине сийхронизации

10 подается тактирующий сигнал, по которому происходит изл«е««ение состояний триггеров 5 выдачи нулей и триггеров 6 выдачи единиц. Съем информации с мажо1

r .и. тарного элемента 1 производится в л«о« л«е««т появления сигнала на шине 10.

Дальнейшую работу устройства рассмот-, рим на примере подачи на его входы произвольнь«х чисел. Предположил«, что на левый (по схеме) вход 11 устройства IIo» дается число 1011, на средний — число

1000, а на правый - число 0111. При подаче на входы 11 старших разрядов приведенных чисел единицы запол«и««аются на левом и среднем (по схеме} триггерах 8, с которых поступают на соответствующие входы мажоритарного элемента

1 и на соответствующие схемы "И" 4, в результате чего на выходе мажоритарного элемента 1 формируется единица, которая поступает на схемы "И" 2 и инвертор 3. На выходе инвертора 3 формирур ется низкий потенц «ал, который запрещает срабатывание схем "И" 4. Левая и средняя схемы "И" 2 закрыты низким сигналом с нулевых выходов триггеров

8, а правая схема "И" 2 под«отовлены к срабатыванию. При поступлении с««гни«ы по шине 10 срабатывает правая схема

"И" 2, которая устанавливает правый триггер выдачи нулей 5 в единичное состонн««е. Так как сигнал по шине 7 поступает один раз при установке устройства в исходное состояние перед ««р««ел«ол« данного числа, то правый триггер 5 будет

««аход«гг«.ся в единичном состочнии ны все врел«««приел«а числа. Единичное состояние право .> триггера 5 выдачи нулей безус; „Ф

««овне «удерживает правый входной тр««гге(8 в пулевом состоянии. В дальнейшем, иезави<:имо от того, как инфррмация будет поступать по правому входу 1 1 правый три«хгер 8 будет находиться в нул»вом состоянии и с едини а«ого выхода его будет выдаваться низкий потенциал, который носту««ыет на правый вход мажоритар4 ного элемента 1 и запрещает срабатыва- ние правой схемы "Итх 4.

Единичное состояние правого триггера

5 выдачи нулей соответствует поступлению минимального числа по правому входу 11, После поступления сигнала по ши не 10 поступает сигнал по шине 9 и подготавливает входные триггеры 8 к приему очередной цифры числа. Вслед за старшим

«0 разрядом числа на входы 11 устройства поступает следующий разряд числа (в данном случае соответствующий нулю во .всех разрядах). При этом состояние три« еров 5 выдачи нулей и триггеров 6

15 выдачи единиц не изменится. Далее в предварительно подготовленные сигналом по шине 9,триггеры 8 поступает третья цифра. После срабатывания левого триггера на левом входе мажоритарного элемента 1 присутствует единичный сигнал, а на среднем и правом — нулевые сигналы, На выходе мажоритарного элемента 1 формируется нулевой сигнал, который запрещает срабатывание схем "И" 2, а чере««инвертор

3 подготавливает к срабатыванию схемы

И" 4. Но разрешение «Ia срабатывание схемы "И," 4 по другому входу поступает только на левую схему "И" 4 от единичного плеча левого триггера 8. С прихо20

30 дом сигнала по шине 10 срабатывает толь ко левая схема "И" 4 и устанавливает левый триггер выдачи единиц 6 в единичное состояние, который в дальнейшем будет безусловно,удерживать левый входной T(I«II гер 8 в единя «««ом состоянии независимо от вида информации, которая псн тупит ио левому входу 11. Единичное состояние невого триггера 6 выдачи единиц соответствует поступлению максимального числа ио

40, левому входу 11. В дальнейшем на выходе мажоритар««ого элемента 1 будут формировосстанавливать истинную информацию в каналах резервированного устройства.

Предмет изобретения

Устройство дня выбора среднего ио ве,;:личине двоичного числа, содержащее входо5

:.ные трштеры, едииич««ые выход I которых соединены с соответствующими входами мажоритарного элене««та, выход которого

::связан непосредственно с первылн«входаI

;ваться сигналы, соответствующие ностуныIowIIM ио среднему входу 11 числу 1000, l которое является средним по вели ««ше, т. е.

4> 0111(10004 1011.

Таким образом, устройство позволяет

44 17 14

5 ми схем "И анализа нулей н через инвертор — с первыми входами схем И" анализа единиц, и триггеры выдачи единиц и нулей, единичные входы которых соединены с выходами соответствующих схем "И" анализа единиц и нулей, о т л и ч а ющ е е с я тем, что, с целью упрощения устройства и расширения функциональных возможностей, в нем единичные и нулевые

6 выходы входных триггеров соединены со вторыми входами соответствующих схем

И анализа единиц и нулей, нулевые входы — с единичными выходами триггеров выдачи нулей, а единичные входы — с еди. ничнымн выходами триггеров выдачи единиц, причем третьи входы схем И" ана лиза нулей и единиц подключены к шине ,синхронизации.

447 (14

Составитель В.Денисов

Тепрел И.Карандашова Корректор А.Степанова

Редактор А.Бер

Предприятие «Патент», Москва, Г-59, Бережковская наб., 24

Заказ а4РО Тираж 624 Подписное о

ЦНИИПИ I îñóäàðñòâåûíîãî комитета Совета Министров СССР по делам изобретений и открытий

Москва. 113035, Раушская наб., 4