Следящий умножитель частоты

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН Ия

К АВТРРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскин

Социалистических

Ресвублик (11) 447721 (61) Дополнительное к авт. свид-ву(22) Заявлено 16.04.73(21) 1913037/18-24 (51) М, Кл.

Q 06 ) 7/16 с присоединением заявки ¹

{23) Приорнтет(43) Опубликовано 25.10.746вллетеиь %39 (4б) Дата опубликования описаиия24.09.75

Геаударетееннвй квинтет

Сената Мнннстрее СЕР не делам нзееретрннй к еткрмтнй (N) УДК

681.335 (088.8) (72) Авторы изобретения

В, С. Гутников, А, Д, Толчинский и А. И. Недашкавский (7l) Заявитель

Ленинградский ордена Ленина политехнический институт им. М. И. Калинина (54) СЛЕЙЯЩИЙ УМНОЖИТЕЛЬ ЧАСТОТЫ

Устройство относится к электроизмери- тепьной и вычислительной техыике.

Известеы умножытель частоты импульсов, выполненный в виде следящей системы с релейным управлением, содержащей фазовый компаратор, интегрирующий усилитель, 1 генератор импульсов управляемой частоты, делитель "частоты, два ключа и разнополярные источники опорного напряжения, под« ключаемые к входу интегратора в зависимости от знака разности фаз входного сит нала обратной связи.

Однако такой умыожитель частоты характеризуется фазовой погрешностью, обусловленной нечувствительностью устройства ld к изменениям фазы входного сигнала в пределах 2й и склонностью к возникновению автоколебаний.

Целью изобретения является повышение точности умыожителя. 20

Это достигается тем, что в устройстве фазовый компаратор выполнен в виде реверсивного счетчика с ключами ыа входах, причем управляющие входы этих ключей соединены с выходами схем ИЛИ, входы, йб.которых подключены к соответствующим

:выходам триггеров реверсивнм о счетчика.

Такое включение позволяет обеспечить ре,лейно-пропорциональный режим работы умножителя частоты.

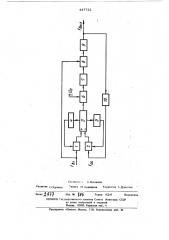

На чертеже изображеыа структурная схема умножителя частоты.

Устройство содержит ключи 1, 2, выходы которых соединены соответственно с суммирующим и вычитаюшим входами реверсивнсн.о счетчика 3. Управляющие входы ключей 1, 2 соединены с выходами схем

ИЛИ" 4, 5, входы которых подключены соответственно к инверсным и прямым выходам триггеров счетчика 3. Прямой выход последнего триггера счетчика 3 подключен также к управпяюшему входу ключа-формирователя 6, ыа сигнальный вход которого подается опорное напряжение - 0

Выход ключа-формирователя 6 соединен с входом интегратора 7, выход которсе о подключен к сигыальыому входу запоминающего элемента 8, соединенного своим управляющим входом с общим входом устройства и сигнальным входом ключа 1.

447721

Выход элемента 8. соединен с входом генератора 9 импульсов управляемой частоты, выход которого подключен к общему выходу устройства и через -делитель част ты 10, осуществляющий деление выходной частоты Х р „на постоянное число М, соединен с сигнальным входом ключа 2.

Устройство работает следующим образом.

В исходном состоянии счетчик 3 обнулен. При этом на управляющий вход ключа 1 с выхода схемы "ИЛИ 4 поступает единичный разрешающий потенциал, ключ 2 закрыт нулевым потенциалом с выхода схемы "ИЛИ 5, и последний триггер счетчика 3 находится в нулевом состоянии, а следовательно, опорное напряжение О не подается на вход интегратора 7. На выходе управляемого генератора 9 формируют» ся импульсы выходной частоты, равной, на"р" ер величине f ИиН .

Входные импульсы частоты 1 „ заполняют счетчик 3, и в некоторый момент времени последний триггер счетчика уста« навливается в единичное состояние, закрывая при этом ключ 1. Интегратор 7 через ключ-формирователь 6 начуйает интегрировать опорное напряжение Ц, что приводит к изменению выходиой частоты управляемого генератора 9.

Поступающие на вычитающий вход счет» чика 3 импульсы обратной связи. частоты компенсируют изменения частоты

В установившемся режиме импульсы частот 1 и f поступают на входы счет6Х чика 3 поочередно. В результате последний триггер счетчика 3 меняет свое состояние с приходом каждого импульса этих частот, т.е. фазовый компаратор начинает улавливать текущее изменение фазы двух импульсных последовательностей 1 и f

ЬХ 0С а следовательно, умножитель переходит на линейный режим работы.

При резком изменении входной частоты реверсивный счетчик 3 устанавливается в состояние, при котором все триггеры переходят в нулевое или единичное положение, т.е. устройство находится в релейном режиме работы, при котором генератор 9 генерирует одно из крайних значений выходф. ной частоты сии„или „<„ до выхода устройства на режим линеййсв о слежения.

Для сглаживания в режиме линейного слежения флюктуацит выходного напряжения интегратора 7 используется запоминающий элемент 8, который с частотой f 8 опрашивает выход интегратора 7 и запоминает его выходное напряжение до прихода очередного импульса частоты

10 Реверсивный счетчик 3 в простейшем случае может представлять собой делитель на два. Для обеспечения сглаживания мгновенных изменений выходной частоты, обусловленных неравномерностью следова-, 15 ния импульсов входной частоты при нали- . чии помех, емкость счетчика 3 может быть выбрана равной 4-8.

Предмет изобретения !

Следящий умножитель частоты, содержащий реверсивный счетчик, ключ-формирователь, сигнальным входом соединенный с источником опорного напряжения, а выходом подключенный через интегратор к сигнальному входу запоминающего элемента, соединенногЬ своим управляющим входом с входом устройства, выход запоминающего элемента подключен к входу генератора управляемой частоты, выход которого соединен с выходом устройства и входом де. лителячастоты, отличающийся тем, что, с целью повышения точности, в него введены две схемы "ИЛИ" и два до»полнительных ключа, сигнальный вход одного из которых соединен с входом устройся ва, à его выход подключен к суммирующему входу реверсивного счетчика, вычитающий вход которого подключен к выходу другого дополнительного ключа, соединенного сигнальным входом с выходом делителя частоты, управлявшие входы дополнитель4> ных ключей соединены с выходами соотвечс ствующих. схем ИЛИ, входы которых

t подключены соответственно к прямым н обратным выходам реверсивного счетчика, выход старшего разряда счетчика подклю5О чен к управляющему входу ключа-формирователя.

447721

Состаззн1c..iз (.КрЗДЦЩЩ Ге" ред М. девитткая Kopperтор A.äçåññ;âà

РедактоР P Кунина

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская иабзз 4

Предприятие «Патент>, Москва, Г-59, Бережковская иаб., 24 заказ gg)Г иза. за Зазрз тараи 624 Попппапоа