Долговременное запоминающее устройство

Иллюстрации

Показать всеРеферат

Ф Фтен- . ;:аале библ.i...

ОП МСАИИ Е

ИЗОБРЕТЕЙ ИЯ

К АБХОРСКОИУ СВИД6ТЙДЬО" ВУ

) 447758

Союз Советских

Социвлистимеских

Ресяубиик

l (61) Зависимое от авт. свидетельства— (22) Заявлено 04.11.72 (21) I844640/?82 (51) М Кл.

&11с 17/00 с присоединением заявки—

Государстоеннмй номнтет

Соввтв Мнннстров СССР ло делан нзооретеннй и отнрытнй (32) Приоритет—

Опубликованй5, 10.74 Бюллетень Мо 39 (45) Дата опубликования описания 15. 12.74. (53) УИК

681. 327. 66(088. 8) В.Д.Антонов, В.В.Батанов, А.М.Иванов, И.ФЛусатов, В.А.Кукуев, !0.В.Работин, Г.К.Сивков, Я.A.Õåòàãóðoâ и В.И.Кузнецова (72) Авторы изобретения (71) Заявитель (Б4) ДОЛГОВРЕМЕННОЕ ЗАПОМИНАК1ЦЕЕ УСТРОЙСТВО

Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых вычис лительных машинах.

Известно долговременное запоминающее устройство, содержащее накопители, соединейные с соотвеиствующими дешифраторами и блоками усилителей считывания, адресный и числовой регистры, соединенные соответственно с дешифраторами и блоком усилителей считывания.

При увеличении информационной емкости этого устройства снижается его быстродействие и надежность

Предлагаемое долговременное запоминающее устройство содкржит блок управления цепями считывания, блок обратной логической связи, блок выходных усилителей, блокй входных элементов "И", дешифратор стробов и элементы "ИЛИ". Дешифраторы накопителей и дешифратор стробов подключены к адресному ре2 гистя sexes блоки входных влеивнl

ToE ° ыходы дешифратора стробов соединены с блоками усилителей считывания, выходы которых под5 ключены через элементы "ИЛИ" к блоку выходных усилителей, соединенному с числовым регистдом.

Блоки входных элементов "И" и блок выходных усилителей подклю1о чены к соответствующим выходам блока управления цепями считыва— ния. Входы блоков входных элементов " И" подключены дополнительно к адресному регистру через блок обратной логической связи.

Такое выполнение УстРойства повышает его быстродействие и надежность.

2О

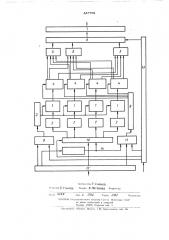

На чертеже изображена блоксхема предлагаемого долговременного запоминающего устройства.

Устройство содержит несколько накопителей 1, каждыи из которых

l подключен к одному из саответст5

20

44 вующих дешифраторов 2 и дешифратору 3. Выходй накопителей подключены к соответствующим блокам усилителей считывания 4.

Одноименные выходи блоков усилителей считывания подключены к соответствующему элементу "ИЛИ" 5.

Выходы элементов "ИЗИ" соединены с блоком выходных усилителей 6, подключенным к числовому регистру

7. Дешифраторы 2, дешифратор З,дешифратор стробов 8, управляющий выбором блока усилйтелей считывания 4, подключены соответственно через блоки входных элементов "И"

9 — П к адресному регистру Е2.

Блок выоднйх усилителеи 6 и блоки вхоцных элементов "И" 9 -П подключены к выходам блока управления цепями считывания 13. Входы блоков входных элементов ™Г 9 и

П соединены,цополнительно с адресным регистром Е2 через блок обратной логической связи I4.

Предлагаемое долговременное запоминающее устройство работает следующим образом. На адреснйй регистр I2 поступает код адреса числовой ячейки одного из накопителей Е„ а на блок управления цепями счйтывания Е3 — сигнал обращения к устройству. Код адреса, устаповившиися на адресном регйстре I2, поступает непосредственно на блоки входных схем 1I" 9-П.

Сигналы с отдельных разрядов эцрасного регистра Е2 через олок обратной логической связи I4 такze поступает на входы блоков вхацных элементов "И" 9 и П.

С выходов блоков входных элементов "И" 9 и ЕО сигналы посту— пают на вхоцы одного из дешифраторов 2 и дешиаратора Э в моменты времени, определяемые поступлением сигналов запуска из блока управления цепями считывания I3, задающего выдачу сигналов запуска.

В соответствии с логикой работы одного из дешифрэторов 2 и один выход деши@ратора 3, благодарн чему выбирается числовая ячейка одного из накопителей Х, сигналы с-IifTLiBBHMH из которой посHB оц lit из 6UQKoH QQNJEITBлей с_#_ITUbH ii>H 4. Работой блоков усиливателей считывания 4 управЗ0

8

+ ляет дешифратор стробов 8, на вход которого поступают сйгналы из блока входных элементов

"И" П. Запуском блока входных влементов "И" II управляет адрес ный оегисто Е2. блок обратной логической связи I4, блок управления цепями считывания 18 При йоявлении сигналов на выхолэх олного из блоков усилителей считывания 4 через элементы ™ИЛИ" 5 на блок выход. ных усилителей 6 поступает код числа, хранившейся в выбранной числовой ячейке одного из накопителей I. Блок выходных усилителей

6 передает код числа на числовой регистр 7 в момент времени, определяемый блоком управления цепями считывания 13.

ПРЕДМЕТ ИЗОБРЕТЕНИЯ

Долговременное запоминающее устройство, содержащее накопители соединенные с соответствующими дъшифраторами и блоками усилителей счйтывания, адресный и числовой регистры, о т л и ч а ю щ е е с я тем, что, с целью повышения быстро действия и надежности работы, оно содеял.жит блок управления цепями считйвания, блок обратной логической связи, блок выходных усилитнлей, блоки входных элементов

"И"< дешифратор стробов и элементы ИЛИ", дешиураторы накопителей и дешифратор стробов подключены к адресному регистру через блоки входных элементов "И", а выходы дешифратора стробов соецинены с блоками усилителей считывания, выходы которых подключены через элементы "ИЛИ" к блоку выходных усилителей, соединенному с числовым регистром; блоки входных элементов "И" и блок выходных усилителей подключены к соответствующим выходам блока управления цепями считывания, а входы блоков входных элемейтов "И" подключены дополнительно к адресному регистру через блок обратноР логической связи.

447758

Составитель Г. С ИВКОВ

Техрел Л.ПОТЯПОВЯ !(оРРек оР ! - 0P Е, ГОНЧВР

Ао55

1!зл. М ЮГ- Тпратк ХЖ. Полиисиое

1!!!1!1!!!И I осучарствсиного комитета Совета Министров (УССР по делаи изобретений и откртятий

Москва, 113035, Раушская наб., 4

11рслприя)ие «!1атеит», Москва, 1 59, Бережковская наб., 24