Модуль коммутации

Иллюстрации

Показать всеРеферат

Q%j

О С " А " Е

ИЗОБРЕТЕН ИЯ (11), 447836

Своз Советских

Сотвеалистииеских

Реслублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства(22) Заявлеио05.07.72 (21К80544Х/26-9 (51) М Кл.

Б 03к, 17/00

Е 04 ) 3/00 с присоединением заявки " (32) ПриоритетОпубликоваи<?5, 10,74Бюллетень № 39 (45)нДата опубликования описания 5,12.7

Гааударстеенный коиетет

Совета Инннетреа СССР ое делам нзебретеннй н открытий (Я} УИК 621,395. 34(088.8) (72) Авторы изобретеиия

В.П. фркиБ (71) Заявитель (54) 1

I—

Изобретение относится к области связи, в частности к пространственно-временным коммутационным системам, базирующимся на линиях с временным уплотнением.

Известны устройства коммутации пространственного типа с синхронным принципом коммутации, которые работают только с устройством управления системы и требу ют б ".тродвйствующих элементов для их реализации.

В предложенном модуле коммутации впервые осуществлена асинхронная пространственная коммутация, которая достигнута путем введения в модуль коммутации блоков памяти, схемы распределения приоритетов и дополнительных адресных шин. Это позволяет снизить требования к быстродействию элементов, упростить пространственную коммутацию и изъять управление модулем коммутации.

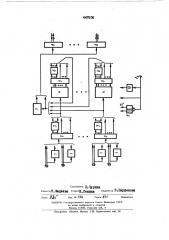

На чертеже изображен предло- женный модуль коммутации»

Он состоит из входных дешифраторов 1 для опознавания информации входных адресно-информационных магистралер, входных регистров 2 для промежуточного хранения коммутируемой информации, двшифраторов 5 для определения н мера выходного регистра, в который необходимо выдать ийформацию, блоков памяти Ф для хранения ин-, формации в процессе асинхронной коммутации, регистров 5 для промежуточного хранения информации, считанной из блоков памяти и подготовленной для коммутации, двшифраторов б для опредвленйя новара выходного регистра в который требуется выдать ин орыацию, схеиы распределения приоритетов 7 для определения очередности обола; жйвания регистров с коммутируемой информацией, выходных регистров 8

l a промежуточного хранения инФо1}447836

3 мации, триггера 9 и схемы Ч Е" 10 для вйработки тактовых импульсов, синхронизирующих рабсеу модуля коммутации. 5

Модуль коммутации рабагает следующим образом. По tn входным адресно-информационным магистралям параллельным кодом поступает информация в сопровождении адресов (номеров} временных позиций выходных уплотненных линий, в которые требуется ее выдать. Если информация принадлежит одной из уплжненных линий, обслуживаемых с помощью модуля коммутации, то дешифраторы 1 опознана ее и производят запись на регистры 2.

Каждый входной регистр 2 поочередно обслуживает две адрвсноинформационные магистрали и выдает их информацию в выходные регистры 8 или записывает в блоки памяти 4, если выходные регистры заняты. Йомер выходного регистра, в который необходимо выдать информацию из входных регистров, определяется дешифраторами 3.

Информация, записанная в бло- „ ки памяти 4, считывается и записывается на регистры 5. П и этом адреса, сопровождающие ин ормацию, поступаи. на дешифраторы . Считывание инфориаци1; из блоков памяти 4 и -апись ее на регистры 5 происходит последовательно по мере выдачи информации на выходные регистры 8. фри этом дешифраторы б определяют номер выходного ре- 40 гистра для запис и информации.

С игналы с выходов де шифрат оров 3 и б и блоков памяти 4, определяющие уровень их заполйения, поступают на схему распределения 45 приоритетов 7, которая вырабатывает сигналы, определяющие очередность обслуживания регистров 2 .1 5 (преимущественно обслуживаютея наиболее ааполненныв блоки памяти). Регистры 8 обслуживают выходные адресно-информационные магистрали модуля коммутации.

Триггер 9 и схема "НЕ" 10 с помощью частоты f< вырабатывают тактовые импульсы %<, синхронизирующие работу всех устройств модуля коммутации.

ПРЕДМЕТ ИЗОБРЕТЕНИЯ

Модуль коммутации, содержащий регистры информации, дешифраторы адреса, триггер тактов и схему

"НЕ", отличающийся тем, что, с целью снижения требованйй к быстродействию элементов и упрощения коммутации, в него введены блоки памяти, схема распределения приоритетов и адресные шины, при этом входные магистрали подключены ко входам первых дешифраторов адреса и регистров информации, выходы которых соединены со входами вторых дешифраторов адреса и блоков памяти, выходы блоков памяти подключейы ко входам схемы распределения приоритетов и вторых регистров информации, а их выходы подклниены ко входам третьих дешифраторов, выходы которых совместно с выходами вторых дешифраторов подключены ко входам схемы распределения приоритетов, а выходы последней совместно с выходами первых и вторых регистров информации соединены со входами третьих регистров информации, к выходам которых подключены выходные магистрали, шина синхронизирующей частоты йодключена ко входу схемы "НЕ", триггеру тактов и ко входам вторйх и третьих двшифраторов, выходы схемы "НЕ" и триггера тактов соединены со входами блоков памяти и регистров информации.

447836

Заказ Я@

Тираж 8Н

Изд. И P 56

Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, П3035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская наб., 24

Составитель В фрщ Н

Редакгорт„ф®ДЕ® щ Техредн Qg g Корректор ВаПИРфОНОЗВ