Двоичный счетчик с контролем ошибок

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и) 448469

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 09. 03.72 (21) 1757305/18-24 с присоединением заявки № (32) Приоритет (51) М. Кл. G 06m 3/12

G 061 11/00

Государственный комитет

Совета Министров СССР по ленам изобретений и открытий

Опубликовано 30.10.74. Бюллетень № 40 (53) УДК 681.326.7 (088.8) Дата опубликования описания 23.06.75 (72) Авторы изобретения

Т. М. Бандзеладзе, P. Д. Джаши, В. М. Завьялов, С. В. Учанейшвили и О. В. Чачанидзе

Тбилисский научно-исследовательский институт приборостроения и средств автоматизации (71) Заявитель (54) ДВОИЧНЫЙ СЧЕТЧИК С КОНТРОЛЕМ ОШИБ

Изобретение относится к области вычислительной техники и может быть использовано в устройствах автоматического управления.

Известен двоичный счетчик с контролем ошибок, содержащий счетную схему на триггерах, схему формирования прогнозируемого признака четности и схему контроля четности единиц.

Однако в таком счетчике при параллельной записи отличного от .нуля числа, начиная с которого требуется пересчет, необходимо формирование признака четности записываемого числа для исключения возможности ложного срабатывания схемы контроля.

Кроме того, недостатком известной схемы является невозможность осуществления контроля реверсивного счетчика, так как схема формирования прогнозируемого признака четности формирует этот признак только на последующее возрастающее число.

Цель изобретения — расширение функциональных возможностей схемы контроля двоичного счетчика, построенного на базе потенциальных логических элементов.

Это достигается тем, что в предлагаемом счетчике выходы «1» всех разрядов вспомогательного регистра и старшего разряда основното регистра соединены с входами схемы контроля на нечетность; схемы «И», соединенные своими выходами с входами установки в «1» и «О» всех разрядов основного регистра, связаны соответственно своими входами с выходами «О» и «1» одноименных разрядов вспомогательного регистра; выходы «1»

5 всех, за исключением старшего, разрядов основного регистра соединены с входом схемы

«И», связанного по выходу с входом установки в «1» триггера того же разряда вспомогательного регистра, и входами схем «И», сое10 диненных выходами с входами установки в

«О» и «1» триггера следующего разряда вспомогательного регистра; выход «1» старшего разряда основного регистра соединен с входом схемы «И» установки в «1» триггера того же

15 разряда вспомогательного регистра; входы схем «И», связанных выходами с входами триггера младшего разряда подключены к инверсному входу счетчика.

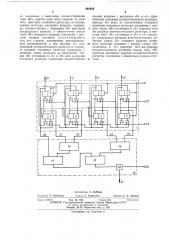

На чертеже показана блок-схема предла20 гаемого счетчика.

Для конкретности рассматривается четырехразрядный счетчик.

Двоичный счетчик 1 на потенциальных логических элементах с последовательным пе25 реносом единиц состоит из основного регистра (верхний ряд триггеров 2 — 5) и вспомогательного регистра (нижний ряд триггеров 6 — 9).

Единичные выходы 10 — 13 триггеров основного регистра являются выходами счетчика, при30 чем 10 — выход первого разряда счетчика, 448469

Зо

3

11 — выход второго разряда и т. д. Схема 14 контроля состоит из схем «ИЛИ» 15 — 18, осуществляющих функцию сложения по модулю

2 и схемы «И» 19, первый из входов .которой подключен к выходу схемы 18, а второй соединен с входной клеммой 20. Результат контроля .работы счетчика (сигнал «Правильно») снимается с выхода 21.

Единичные выходы 22 — 25 триггеров вспомогательного регистра счетчика подключены к входам схемы контроля на нечетность единиц. К схеме контроля подключен единичный выход 26 триггера высшего разряда основного регистра счетчика. Число контролируемых триггеров равно пяти. В общем случае число контролируемых триггеров равно а+1 (n — число разрядов счетчика).

Счетчик работает следующим образом, В исходном положении все триггеры основного регистра и триггер первого разряда вспомогательного регистра устанавливаются в состояние «О», а остальные триггеры вспомогательного регистра — в состояние «1». Таким образом, при установке «О» число триггеров вспомогательного регистра, установленных в состояние «1», равно трем.

Так как на входы схемы 14 контроля поступает нечетное число единиц, на первом входе схемы «И» 19 устанавливается «1». Таким образом, при появлении импульса «Опрос» на входе 20 и выходе 21 оказывается «1», что соответствует правильности работы счетчика.

Прямое и инверсное значения входного сигнала подаются на входы 27 и 28 соответственно.

При поступлении:первого входного сигнала триггер первого разряда основного регистра устанавливается в состояние «1», а триггер второго разряда вспомогательного регистра— в состояние «О». После снятия входного сигнала триггер первого разряда вспомогательного регистра перебрасывается в состояние «1».

Таким образом, число контролируемых триггеров, изменивших свое состояние после окончания действия первого входного сигнала, равно двум и следовательно нечетность единиц, подаваемых на входы схемы 14, сохраняется.

С приходом второго входного сигнала триггер первого разряда основного регистра устанавливается в состояние «О», триггер второго разряда этого же регистра — в состояние «1», а триггер третьего разряда вспомогательного регистра — в состояние «О». После снятия входного сигнала триггер первого разряда вспомогательного регистра перебрасывается в состояние «О». Как и в первом случае, изменяют свое состояние только два триггера вспомогательного регистр а, т. е. нечетность числа единиц, подаваемых на входы схемы контроля, сохраняется. Отсюда следует чт число триггеров вспомогательного регистра, изменяющих свое состояние после каждого очередного входного сигнала, не меняется и равно двум. Исключение составляет только тот момент, когда устанавливается в единичное состояние триггер высшего разряда основного регистра.

В этом случае изменяет свое состояние только один триггер вспомогательного регистра, так как четвертый разряд является последним в счетчике и следовательно отсутствует перенос на триггер вспомогательного регистра следующего разряда, Однако нечетность единиц не нарушается, потому что число триггеров, изменивших свое состояние, остается равным двум, вследствие того, что триггер высшего разряда основного регистра входит в число контролируемых триггеров..Таким образом, при правильной работе счетчика число единиц, подаваемых на входы схемы контроля, сохраняется нечетным и на первый вход схемы «И» 19 подается «1», что свидетельствует о правильности работы счетчика. При нарушении работы счетчика (ложном срабатывании или выходе из строя любого из триггеров) нечетность числа единиц, подаваемых на схему контроля, нарушается и отсутствие «1» на входе 21 сигнализирует о нарушении работы счетчика.

Задержка времени поступления сигнала

«Опрос» на вход 20 относительно сигнала на входе 27, запускающего счетчик, определяется суммой трех составляющих

"s — уст+ п + ск где ту„— время окончания распространения переносов и переключения последнего каскада счетчика; тур время переключения одного триггера; т, — время протекания переходного процесса в схеме контроля.

Счетчик содержит четное число разрядов (n=4).

При нечетном числе разрядов счетчика сохранения контроля по нечетному числу единиц следует вместо единичного выхода 26 триггера высшего разряда основного регистра к схеме 14 контроля подключить нулевой выход 29 того же триггера.

Приведенная на чертеже схема контроля работы счетчика пригодна для контроля работы реверсивного счетчика. В этом случае к схеме 14 контроля подаются единичные выходы всех триггеров вспомогательного регистра и единичный (или нулевой) выход высшего разряда основного регистра реверсивного счетчика.

Эту схему можно использовать для контроля работы счетчика с параллельной за писью числа, начиная с которого требуется счет.

Предмет изобретения

Двоичный счетчик с контролем ошибок, содержащий и-разрядные основной и вспомогательный регистры, схему контроля на нечетность с (n+ I ) входами и схемы «И», входы установки в «О» и в «1» всех триггеров счетчи448469

28

Составитель А. Лебедев

Техред 3, Тараиеико

Редактор Т. Рыбалова

Корректор Л. Орлова

Заказ 1103/11 Изд. № 1223 Тираж 624 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Я-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 ка соединены с выходами соответствующих схем «И», причем один вход каждой из схем

«И», триггеров основного регистра, за исключением триггера младшего разряда, соединены соответственно с выходами «О» триггеров предыдущего разряда, а аналогичные входы схем «И» младшего разряда соединень1 с прямым входом счетчика, отличающийся тем, что, с целью расширения функциональных возможностей, в нем выходы «1» всех разрядов вспомогательного регистра и старшего разряда основного регистра соединены с входами схемы контроля на нечетность; схемы «И» установки в «1» и «О» всех разрядов основного регистра соединены соответственно

II 1

I !

1 !

1 своими входами с выходами «О» и «1» одноименных разрядов вспомогательного регистра; выходы «1» всех, за исключением старшего, разрядов основного регистра соединены с вхо5 дом схемы «И» установки в «1» триггера того же разряда вспомогательного регистра, и входами схем «И» установки в «О» и «1» триггера следующего разряда вспомогательного регистра; выход «1» старшего разряда основ10 ного регистра соединен с входом схемы «И» установки в «1» триггера того же разряда вспомогательного регистра; входы схем «И» триггера младшего разряда вспомогательного регистра соединены с инверсным входом счет15 чика.