Устройство для синхронихации импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (»1 448585

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 05.01.73 (21) 1873992/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 30.10.74. Бюллетень № 40

Дата опубликования описания 10.06.75 (51) М. Кл. Н 03k 5/156

Государственный комитет

Совета Министров СССР о делам изобретений и открытий (53) УДК 621.373(088.8) (72) Авторы изобретения

О. Г. Светников, В. Г. Чибисов (71) Заявитель Особое конструкторское бюро вычислительной техники Рязанского радиотехнического института (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ИМПУЛЬСОВ

Изобретение относится к области импульсной техники.

Известно устройство для синхронизации импульсов, содержащее триггер, схему совпадения, логические схемы «ИЛИ», «И — НЕ» и инвертор.

Целью изобретения является уменьшение критичности к длительности импульсов.

Эта цель достигается за счет введения в предложенное устройство дополнительного триггера и дополнительной схемы совпадения.

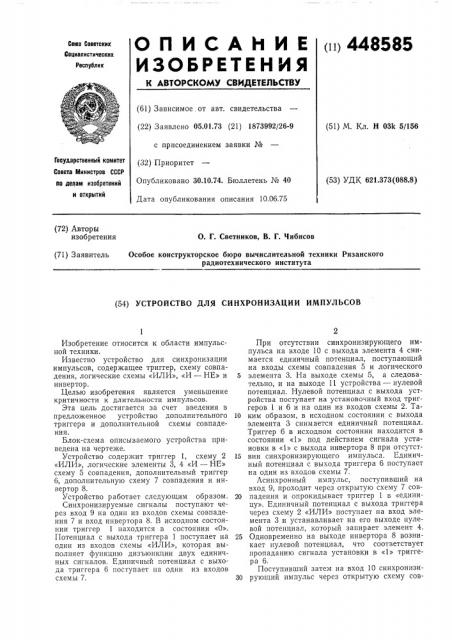

Блок-схема описываемого устройства приведена на чертеже.

Устройство содержит триггер 1, схему 2

«ИЛИ», логические элементы 3, 4 «И — НЕ» схему 5 совпадения, дополнительный триггер

6, дополнительную схему 7 совпадения и инвертор 8.

Устройство работает следующим образом.

Синхронизируемые сигналы поступают через вход 9 на один из входов схемы совпадения 7 и вход инвертора 8. В исходном состоянии триггер 1 находится в состоянии «О».

Потенциал с выхода триггера 1 поступает на один из входов схемы «ИЛИ», которая выполняет функцию дизъюнкции двух единичных сигналов. Единичный потенциал с выхода триггера 6 поступает на один из входов схемы 7.

При отсутствии синхронизирующего импульса на входе 10 с выхода элемента 4 снимается единичный потенциал, поступающий на входы схемы совпадения 5 и логического

5 элемента 3. На выходе схемы 5, а следовательно, и на выходе 11 устройства — нулевой потенциал. Нулевой потенциал с выхода устройства поступает на установочный вход триггеров 1 и 6 и на один из входов схемы 2. Та10 ким образом, в исходном состоянии с выхода элемента 3 снимается единичный потенциал.

Триггер 6 в исходном состоянии находится в состоянии «1» под действием сигнала установки в «1» с выхода инвертора 8 при отсутст15 вии синхронизирующего импульса. Единичный потенциал с выхода триггера 6 поступает на один из входов схемы 7.

Асинхронный импульс, поступивший на вход 9, проходит через открытую схему 7 сов20 падения и опрокидывает триггер 1 в «единицу». Единичный потенциал с выхода триггера через схему 2 «ИЛИ» поступает на вход элемента 3 и устанавливает íà его выходе нулевой потенциал, который запирает элемент 4.

25 Одновременно на выходе инвертора 8 возникает нулевой потенциал, что соответствует пропаданию сигнала установки в «1» триггера 6.

Поступивший затем на вход 10 синхронизиЗО рующий импульс через открытую схему сов448585

Корректоры: Е. Давыдкина и В. Дод

Техред Т. Курилко

Редактор В. Левятова

Заказ 1333/11 Изд. ¹ 1222 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 падения 5 проходит на выход устройства, перебрасывает триггер 1 в исходное состояние, а триггер б в состояние «0» и поддерживает единичный уровень на время действия синхронизирующего импульса на одном из входов схемы 2. При этом нулевой потенциал с триггера 6 закрывает схему 7 совпадения, запрещая формирование сигнала установки в

«1» триггера 1. Таким образом устраняется влияние длительности входного синхронизируемого импульса на работу схемы. По окончании синхронизирующего и синхронизируемого импульсов схема возвращается в исходное состояние.

Предмет изобретения

Устройство для синхронизации импульсов, содержащее триггер, выход которого подключен к одному из входов схемы «ИЛИ», а вход соединен с выходом схемы совпадения, на входы которой поданы сигналы с логических элементов «И вЂ” HE», отличающееся тем, 5 что, с целью уменьшения критичности к длительности импульсов, в него введены дополнительный триггер, дополнительная схема совпадения и инвертор, причем выход дополнительной схемы совпадения соединен с одlO ним из входов триггера, а один из ее входов соединен с выходом дополнительного триггера, входы которого соответственно соединены с выходом схемы совпадения и через инвертор со входом устройства, при этом второй

15 вход дополнительной схемы совпадения соединен со входом устройства.