Выходной каскад

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и) 448605

ИЗОБРЕТЕНИЯ

Савв 6аввтских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 12.02.73 (21) 1881714/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 30.10.74. Бюллетень № 40

Дата опубликования описания 25.06.75 (51) М. Кл. H 03k 21/10

Государственный комитет

Совета 1йииистров СССР по делам изобретений и открытий (53) УДК 621.374.3 (088.8) (72) Авторы изобретения

В. М. Тафель и В. М. Эйдельнант (71) Заявитель (54) ВЫХОДНОЙ КАСКАД

+— з т1вкл — ввкл в авыкл выкл

Изобретение относится к импульсной технике и может быть использовано в качестве формирователя мощных бинарных сигналов.

Известен выходной каскад, содержащий управляющий и выходной транзисторные ключи, включенные по схеме с общим эмиттером, и эмиттерный повторитель, выход которого подключен к коллектору транзистора выходного ключа, а вход — к выходу управляюще- 10

ro ключа.

Этот каскад не исключает сквозного тока.

Цель изобретения — устранение сквозного тока.

Для этого в каскад введены схемы «И» и 15

«ИЛИ» и элемент задержки, выход которого подключен ко входам упомянутых схем «И» и «ИЛИ». Вторые входы схем «И» и «ИЛИ» объединены со входами элемента задержки, а выходы соединены со входами управляющего 20 и выходного ключей соответственно.

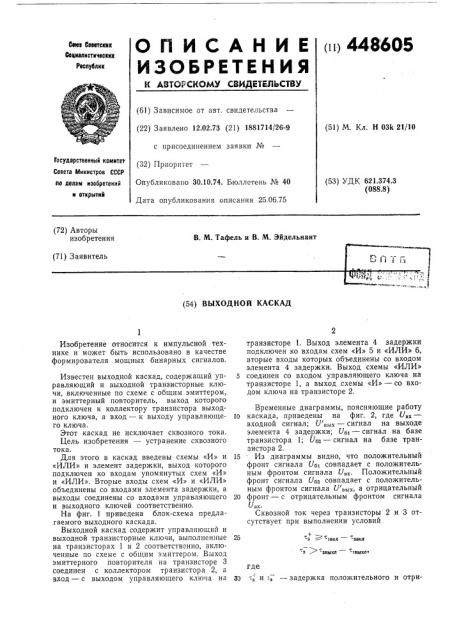

На фиг. 1 приведена блок-схема предлагаемого выходного каскада.

Выходной каскад содержит управляющий и выходной транзисторные ключи, выполненные 25 на транзисторах 1 и 2 соответственно, включенные по схеме с общим эмиттером. Выход эмиттерного повторителя на транзисторе 3 соединен с коллектором транзистора 2, а

Вход — с выходом управляющего ключа на Зз транзисторе 1. Выход элемента 4 задержки подключен ко входам схем «И» 5 и «ИЛИ» 6, вторые входы которых объединены со входом элемента 4 задержки. Выход схемы «ИЛИ» соединен со входом управляющего ключа на транзисторе 1, а выход схемы «И» — со входом ключа на транзисторе 2.

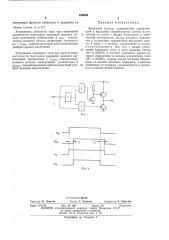

Временные диаграммы, поясняющие работу каскада, приведены на фиг. 2, где U»â€” входной сигнал; U „„„; — сигнал на выходе элемента 4 задержки; Uo< — сигнал на базе транзистора 1; Ров — сигнал на базе транзистора 2.

Из диаграммы видно, что положительный фронт сигнала Uo< совпадает с положительным фронтом сигнала U». Положительный фронт сигнала Поз совпадает с положительным фронтом сигнала U а отрицательный фронт — с отрицательным фронтом сигнала /вкСквозной ток через транзисторы 2 и 3 отсутствует при выполнении условий где.

-., и:, — задержка положительного и отри448605

Г1редмет изо бр ете ни я

@l/Z. 7 À (Ьюх (ггиг. 2

Составитель Еркин

Техред Т. Курилко

Корректор 3. Тарасова

Редактор В. Левитов

Заказ 1112/16 Изд. № 1227 Тираж 811 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, ?К-35, Раушская иаб., д. 475

Типография, пр. Сапунова, 2 цательного фронтов элементом 4 задержки (в общем случае -,++ т,).

Устранение сквозного тока при включении достигается благодаря задержке момента начала включения транзистора 2 т2„л относительно момента начала включения транзистора 1 т(вкл, компенсирующей неблагоприятный разброс времен включения.

Устранение сквозного тока при выключении достигается благодаря задержке момента выключения транзистора 1 т1выкл относительно момента начала выключения транзистора 2 т2выкл компенсирующей неблагоприятный разброс времени выключения.

Выходной каскад, содержащий управляющий и выходной транзисторные ключи, вклю5 ченные по схеме с общим эмиттером, и эмиттерный повторитель, выход которого подключен к коллектору транзистора выходного ключа, а вход — к выходу управляющего ключа, отличающийся тем, что, с целью устра10 нения сквозного тока, в него введены схемы

«И» и «ИЛИ» и элемент задержки, выход которого подключен ко входам упомянутых схем

«И» и «ИЛИ», вторые входы которых объединены со входом элемента задержки, а выходы

15 соединены со входами управляющего и выходного ключей соответственно.