Аналого-цифровое множительно-делительное устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (11) 449445

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) З „, 06.О4.73(21) 1904421 26-9 с присоединением заявки -(32) Приоритет (51) М. Кл.

НОЗ к 13/20

Go6 7/14

Гасударственный комитет

Совета Министров СССР по деяам изобретений и отирытий

ОпубликованоО5.11.74. Бюллетень № 41 (М) УЙК

Дата опубликования описания 21.04.75

681.325 (О88,8) (72) Авторы изобретения

В.Д.циделко и В.А.Тесленко

Киевский ордена Ленина политехнический институт им.5О летия

Великой Октябрьской социалистической революции

1 (71) Заявитель

АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ

УСТРОЙСТВО (54) Изобретение относится к электроизмерительной технике.

Известны аналого-цифровые множительноделительные устройства, содержашие нуль-орган, входы которых подключены к выходу генератора пилообразного напряжения, выполненному на интеграторе, входы которого через соответствующие ключи подключены к источникам разнополярных опорных напряжений, выходы нуль органов соединены с одними входами соответствую. ших схем "И, реверсивный счетчик, генератор прямоугольных импульсов, соединенный со входом вентиля, блок управления.

Предлагаемое устройство отличается тем, что, с целью расширения функциональ ных возможностей, в него введены две дополнительные схемы "И", две схемы

"ИЛИ", дополнительный нуль-орган, схемы задержки и функциональный измерительный частотный преобразователь, вход которого подключен к выходу интегратора и входу дополнительного нуль-органа, а выход через схемы задержки соединен со вторыми входами соответствуюших схем

"И" и непосредственно с одними входами двух дополнительных схем "И, вторые входы которых подключены к выходу блока управления, а выходы - к одним входам двух схем ИЛИ", вторые входы которых подключены к выходу вентиля, а остальные соединены соответственно с выходами двух групп нуль-органов. Выходы

10 схем ИЛИ" через реверсивный счетчик подключены к блоку управления.

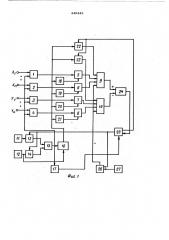

На фиг.1 представлена блок-схема множительно-делительного устройства; на фиг.2 приведены временные диаграммы, 15 поясняющие работу схемы.

Выходы нуль-органов 1-4 через схемы

"И" 5- 8 соединены со входами схем

ИЛИ" 9,10. Источники опорных напряжений 11 и 12 через ключи 13 и 14 связаны

20 со схемой "И 15 (интегратором). Выход схемы "И" 15 соединен со входами функционального измерительного частотного преобразователи (ФИЧП) 16 и нульорганов 1 - 4,17. Выход источника

25 опорного напряжения 12 подключен ко второцу выходу функционального измеря тельного частотного. преобразователя 16, выход которого через схемы задержки 18.

21 и схемы "И 5 - 8,22,23 соединен со схемами ИЛИ 9, 10: Выходы схем

"ИЛИ 9, 10 .через реверсивный счетчик

24 подключены к блоку управления 25, выходы которого соединены с ключами

13, 14, схемами "И 22, 23 и вентилем 26. Генератор прямоугольных импульсов 27. через вентиль. 26 подключен к схемам "ИЛИ 9 и 10, а выход нульоргана 17 подключен к блоку управления

25.

Предлагаемое множительно-делительное устройство выполняет операцию типа

К их -".ф -.

" ) х Дх". > 9 П т.ю

Операции умножения и делении заменяется логарифмированием, сложением и вычитанием. с последующим антилогарифмированием:

Работает устройство следующим образом.

В исходном состоянии на входы нульорганов 1-4 поданы входные величины

Х Х ". Х ) У * У -" Уп .

1 2 ключи 13,14 закрыты. По команде "пуск с блока управления 25 открывается ключ 13, и напряжение У от источника о опорного напряжения 12 поступает на вход интегратора 15.

Выходное напряжение интегратора 15 подается на вторые входы нуль-органов 1 .4 и на вход функционального измерительного частотного преобразователя 16, выходная частота которого обратно пропорциональна времени.

Импульсы с преобразователя 16 подаются на входы линий задержки 18-21, которые задерживают импульсы íà speMs

9 о о /с

L xf p xg p $4X p &JJg)" у + р но не превышающее времени, соответствуц щего периоду его максимальной частоты.

Сдвинутые во времени импульсы через схемы И" 5-8 и схемы "ИЛИ 9,10 поступают на соответствующие входы реверсивного счетчика 24. Импульсы

Х, Х,,..., Х со схем "И" Р,6, управляемых нуль-органами 1,2 йодаются на суммирующий вход реверсивного счетчика

24, а импульсы У, У,..., У ь со схем

И 7,8, управляемых нуль-органами 3,4на вычитающий вход. Как только выход» ное напряжение интегратора достигает зна чения любой .входной величины (Х „, Xe

У,..., У щ ), соответствующий нуль-орган .1О прекращает поступление импульсов на счетчик через схему И", с которой он соединен (фиг.2).

После того как сработают, все нульорганы, в реверсивном счетчике 24 om!

15 зывается число .

/ /. у я хх+ +- + «хх N «д ". Ма г,+... „-е -е .—., .—. юэ. чл Антилогарифмирование в устройстве,. выйолняют генератор импульсов 27, схемы И" 22,23, вентиль 26, нуль-орган

17, источник опорного напряжения 11 и ключ 13. р По команде с. блока управления 2.5.,"

: открывается .ключ 14 и напряжение от источника 12 подается на. интегратор 15.

При этом нуль-орган 17 отключен и включены .схемы "И" 22,23.. С функциоЗО нального измерительного частотного преобра, зователя 16 импульсы поступают через схему И 22 или И 23 и схемы ИЛИ 9,10 на (+) или (») реверсивного счетчика 2.4 в. зависимости от знака получен.35 ного логарифма и сйисывают число At%

Выходная..частота функциональноГо измерительного частотного преобразователя, как и при логарифмировании, обратно пропорциональна времени. Количество

4О импульсов, поступающих на вход счетчика

24, определяется из уравнения

«»= J f(k)dt= 0,. х -ЬАн при =1 и= ЕЬ

При переходе счетчика 24 через нуль блок управления 25 выдает команду, по которой схема И (22 или 23), и

50 ключ 14 закрываются, включаются нульорган 17, ключ 13 и вентиль 26. В этот момент времени Фх=й» т.е. tx-- 6„Х

55 и, следовательно, »-х=Е

449445 т.е. в этот момент напряжение на выходе интегратора 15 ио у

Теперь на вход интегратора подается с источника напряжения 11 напряжение противоположной полярности, и напряжение на его выходе понижается. При этом от генератора 27 через вентиль 26 и схему

"ИЛИ (9 или 10) на счетчик 24 посту- щ лают импульсы с частотой, f . Как только напряжение на выходе интегратора 15 достигает нулевого уровни, нульорган 17 через блок управления 25 закрывает вентиль 26. В счетчик 2.4 записы- д вается число

Таким образом, предлагаемое устройство позволяет выполнять операции лога- 20 рифмирования и потенпиирования за два такта. На его базе можно строить разнообразные функциональные преобразователи, в частности множительно-делительные

I устройства. 25

Предмет изобретения

Аналого-m $poaoe множительно-дели- тельное устройство, содержащее нуль- 39 органы, входы которых подключены к выходу генератора пилообразного напряжения, выполненному на интеграторе, входы которого через соответствующие ключи подключены к источникам разнополярных опорных напряжений, выходы нуль-органов соединены с одними вхоI дами соответствующих схем И, pesepсивный счетчик, генератор прямоугольных . импульсов, соединенный со входом вентиля, блок управления, о т л и ч а ющ е е с;я тем, что, с целью расширении

: функциональных возможностей, в него введены две дополнительные схемы И, две схемы ".ИЛИ, дополнительный нуль-орган, схемы задержки и функциональный измерительный .частотный

1 преобразователь, вход которого подключен к выходу интегратора и входу дополнительного нуль-органа, а выход через схемы задержки соединен со вторыми входами соответствующих схем И" и непосредственно- с одними входами двух дополнительных схем И", вторые входы которых подключены к выходу блока управления, а выходы - к одним входам двух схем ИЛИ, .вторые входы которых подключены к выходу вентиля,. а остальные соединены соответственно с выходами двух групп нуль-органов, выходы схем

"ИЛИ через реверсивный счетчик подклю чены к блоку управления.