Устройство для контроля дешифраторов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (11) 45ol75

Союз Сеевтскнх

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 11.05,73 (21) 1916096!26-9 ,с присоединением зая вки № (32) Приоритет

Опубликовано 15.11.74. Бюллетень № 42

Дата опубликования описания 24.03.75 (51) M. Кл. G 06f 11 00

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 681.3.055 (088.8) (72) Авторы изобретения

Ю, Г. Кожевников и О. А. Летуновский (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДЕШИФРАТОРОВ

Изобретение относится к области автоматHKIH и вычислительной темники.

Известны устройства для контроля дешифраторов, содержащие по две диодные ячейки, подключен ные в определенном .порядке .к выходам дешифратора, а также логические схемы «НЕ», позволяющие обнаруживать,появление ложных сигналов и отсутствие истин ного сигнала .на выходе дешифратора. Ложный сигнал обнаруживается тогда, когда он уже существует на выходе дешифратора, а это часто бывает недопустимо и требует допол нительных устройств для защиты от ложных сигналов, В целях расширения функциональных возможностей в,предлагаемом устройстве,к каждому выходу дешифратора подключена ячейка, представляющая собой схему совпадения и имеющая трансформаторную связь с последующей ячейкой согласно извеспной последователыности возбуждения, выходов дешифратора. На,выходе ячейки .может .появиться сигнал лишь в том случае, если совпадут во времени сигналы на соответствующем выходе дешифратор а и обмотке связи предыдущей ячейки,при ее выключении.

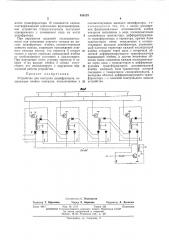

На чертеже показа на схема .предлагаемого устройства.

Устройство содержит дешифратор 1, ячейки контроля 2 и ячейку контроля нормального функционирования 3.

Ячейка 2 содержит последовательно вклю5 ченные транзистор 4, дифференцирующий трансформатор 5, имеющий обмотку связи 6 и выходную обмотку 7, и тиристор 8. Диоды

9 и 10 служат для отсечки импульсов отрицательной полярности соответствующих обмоток.

10 Ячейка 3 состоит из транзисторного ключа 11 и импульсного трансформатора 12;

Устройство работает следующим образом.

При .правильной работе дешифратора 1 в возбужденном состоянии находится только

15 оди|н выход, при этом транзистор 4 и тиристор

8 соответствующей ячейки открыты и на ее выходе существует исти нный сигнал.

Согласно принципу работы дешифратора при .возбуждении следующего выхода сигнал

20 с прерыдущего, ранее возбужденного, выхода снимается и транзисторы соответствующих ячеек принимают состояния согласно выходам дешифратора. В момент выключения транзистора предыдущей ячейки на обмотках 6 и 7

25 появляются импульсы, один из которых включает т иристор 8 следующей ячейки и на ее выход подается истинный сигнал, а другой импульс .поступает на ячейку 3 и при совпадении его с синхроимпульсом на выходной об450175

Вид

Составитель С. Поликарпов

Редактор T. Юрчикова Техред E. Борисова Корректор Л. Денисова

Заказ 684/7 Изд. № 1119 Тираж 624 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-Зо, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 мотке трансформатора 12 появляется сипнал, подтверждающий нормальное функцио нирование устройства. Синхроимпульсы поступают одновременно с изменением кода на входе дешифратора.

При нарушении заданной последовательности или появлении ложного сигнала isa выходе дешифратора ячейка, соответствующая дан ному выходу, запрещает прохождение ложного сигнала потому, что тиристор 8 открыт только в случае перехода предыдущей ячейки из возбужденного состояния в выключенное.

При нарушении этого условия тиристор 8 закрыт и на выходе ячейки 3 сипнал отсутствует, что сигнализирует о нарушении нормальной работы устройства, Предмет изобретения

Устройство для контроля дешифраторов, содержащее ячейки контроля, подключенные к соответствующим выходам дешифратора, о тл и ч а ю щ е е с я тем, что, с целью расширения функциональных возмож ностей, ячейки контроля выполнены в виде последовательно

5 соединенных транзистора, дифференцирующего трансформатора и тиристора, причем базы транзисторов ячеек подключены к соответствующим выходам дешифратора, управляющий электрод тиристора каждой последующей

10 ячейки соединен через диод с вторичной обмоткой дифференцирующего трансформатора предыдущей ячейки, а другие вторичные обмотки ячеек соединены каждая, последовательно через диод с транзистором и дифференци15 рующ им трансформатором дополнительной ячейки контроля, база транзистора которой соединена с генератором синхроимпульсов, а выходная обмотка дифференцирующего трансформатора — с,клеммой контрольного выхода

20 устройства.