Устройство поэлементного фазирования приемников дискретных сигналов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

4Ь0ЗЛ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства 267674 (22) Заявлено 25.12.72 (21) 1862004/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 15.11.74. Бюллетень № 42

Дата опубликования описания 24.06.75 (51) М. Кл. H 041 7/02

Государственный комитет

Совета Министров СССР по делам изобретений н открытий (53) УДК 621.391.833. .4 (088.8) (72) Авторы изобретения

Б. И. Авербух, Ю. Б. Ьалтер, В. Л. Ройзии и А. И. Трест (71) Заявитель

Одесский филиал Центрального конструкторского бюро (54) УСТРОИСТВО ПОЭЛЕМЕНТНОГО ФАЗИРОВАНИЯ

ПРИЕМНИКОВ ДИСКРЕТНЬ!Х СИГНАЛОВ

Изобретение относится к области передачи дискретной информации по каналам связи.

Известно устройство поэлементного фазирования приемников дискретных сигналов, содержащее входное устройство, селектор запаздывающих значащих моментов, селектор опережающих значащих моментов, делитель частоты, сравнивающее устройство, задающий генератор, элемент задержки на длительность половины рабочей посылки н управляющий элемент.

Однако в известном устройстве при поступлении от передатчика сигналов с постоянными преобладаниями, превышающими 50%, возможно устойчивое ложное фазирование с ошибкой в 180 .

В этом случае «О» системы фазирования совмещается не с математическим ожиданием девиаций значащих моментов, а с положением, отличающимся от него на величину, равную 0,5 то, где то — длительность идеального значащего интервала.

Под «О» устройства фазирования в установившемся режиме понимается формируемый системой поэлементного фазирования импульс, соответствующий моменту времени, который определяет границу между зонами запаздывания и опережения значащих моментов. В измерительном приборе этот момент времени принимается за начало отсчета.

Таким образом, ложное фазирование исключает достоверный прием в приемниках

5 дискретных сигналов и достоверный отсчет в измерителях краевых искажений.

С ц-. 1ью снижения возможности ложного фазнрования приемников дискретных сигналои в предлагаемом устройстве выход вход10 ного блока подключен к дополнительному входу делителя частоты через последовательно соединенные схему «И», счетный триггер и схему «И — НЕ», кроме того, два дополнительных выхода входного блока подключены

15 соответственно к установочному входу счетного триггера и к запрещающему входу схемы «И — НЕ», к двум другим входам которой подключены дополнительные выходы делителя частоты, один из которых одновременно

20 подключен к управляющему входу схемы «И».

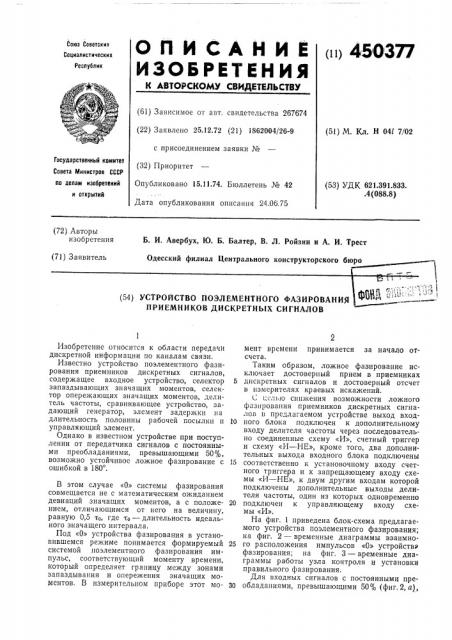

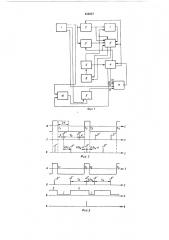

На фиг. 1 приведена блок-схема предлагаемого устройства поэлементного фазирования; на фиг. 2 — временные диаграммы взаимно25 ro расположения импульсов «О» устройство фазирования; на фиг. 3 — временные диаграммы работы узла контроля и установки правильного фазирования.

Для входных сигналов с постоянными пре30 обладаниями, превышающими 50% (фиг.2, а), 450377

35 после установления устойчивого состояния в системе фазирования возможно два положения импульсов «О» устройства относительно входных сигналов.

На фиг. 2, б показано правильное положение импульсов «О». При величине преобладания 2o импульс «О» устройства отстоиг на величину о от значащих моментов различных полярностей.

На фиг. 2, в показано неправильное положение импульсов «О». При той >ке величине преобладаний 2о импульс «О» отстоит на величину 0,5 то — о от значащих моментов разл ич ны х пол я р и остей.

При правильном фазировании число импульсов «0», укладывающихся на длительности единичного значащего интервала входного сигнала любой полярности (момент времени t — tq либо tq — ts), равно нулю либо двум.

При неправильном фазировании на длительности единичного значащего интервала входного сигнала укладывается один импульс «О».

Предлагаемое устройство основано на просчете числа импульсов «О» на длительности единичного значащего интервала.

Предлагаемое устройство содержит (фиг. 1) входной блок 1, селектор 2 запаздывающих значащих моментов, селектор 3 опережающих значащих моментов, делитель частоты 4, сравнивающий блок 5, задающий генератор

6, элемент задержки 7 на длительность половины рабочей посылки, управляющий элемент 8, а также счетный триггер 9, схему

«И» 10, схему «И — НЕ» 11.

Устройство работает следуюшим образом.

Пусть через некоторое время после подачи сигнала (фиг. 3, а) на входном блоке 1 наступило устойчивое состояние системы фазировапия, соотье гствующее ложному захвату (фиг. 3, б).

В момент времени 1 импульс из входного блока, соответствующий значащему моменту, устанавливает счетный триггер 9 по установочному входу в состояние I, запрещающее по входу 12 прохождение сигналов через схему «И — НЕ» 11.

С этого же момента времени до момента времени tq сигнал со входного блока разрешает прохождение импульсов «О» через схему «И» 10 на вход счетного триггера.

В данном случае до момента Времени tp нй счетный вход триггера 9 поступает только один счетный импульс. Триггер 9 устанавливается в состояние II, разрешающее прохождение сигналов через схему «И — НЕ» 11 по входу 12.

На вход 13 схемы «И — НЕ» 11 поступает разрешение прохождения сигнала в момент времени t — 4. Импульс «О» поступает от делителя частоты 4 на вход 14 схемы

«И — НЕ» 11.

По входу 15 разрешается срабатывание схемы «И — НЕ» 11 только в том случае, когда значащий интервал, на длительности которого производится счет импульсов, «О», является единичным интервалом.

Таким образом, при поступлении импульса «О» на интервале времени tq —.t4 (момент времени 4) на схему «И — НЕ» 11 импульс с выхода схемы (фиг. 3, г) устанавливает делитель частоты в положение, сдвинутое относительно «О» на величину, равную 0,5 то, что равносильно мгновенному повороту фазы на

180 . В дальнейшем фазирование будет правильным. Триггер 9 (фиг. 3 б, в) на интервале времени t4 — 4 изменяет свое состояние два раза, т. е. запрещает прохождение сигналов через схему «И — НЕ» 11 на интервале вреMeHH tg — t6, Таким образом, при правильном фазировании импульсы на выходе схемы «И — НЕ»

11 отсутствуют.

Предмет изобретения

Устройство поэлементного фазирования приемников дискретных сигналов по авт. св № 267674, отличающееся тем, что, 40 целью снижения возможностей ложного фзирования, выход входного блока подключе к дополнительному входу делителя частоть через последовательно соединенные схему

«И», счетный триггер и схему «И — HE», 45 кроме того, два дополнительных выхода входного блока подключены соответственно к установочному входу счетного триггера и к запрещающему входу схемы «И — HF»„ к двум другим входам которой подключены

50 дополнительные выходы делителя частоты, один из которых одновременно подключен к управляющему входу схемы «И».