Распределитель импульсов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ нн„„.„

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (б)) Зависимое от авт. свид-ва (22) Заявлено 24.07.72 (21) 1812678/18-24 (51) М. Кл. Q 06 х 1/04 с присоединением заявки _#_å— (3 2 )Прно рите твЂ

Гасударственный иамитет

Совета Министров СССР оо делам изооретений и отирытий (43) Опубликовано 25.11.74,Бюллетень go 43 (53) УДК 681,325.5 (088.8) (45) Дата опубликования описания 18.06.75 (72) Авторы изобретения

В. A. Грехнев и В. Т, Тряпицын (71).Заявитель (54) РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ

Изобретение относится к вычислительной технике и предназначено для распределения сигналов тактовой частоты последовательно по Гтт выходным шинам.

Известен распределитель импульсов, содержащий матрицу схем И-НЕ, две груп. пы схем И-ИЕ и два кольцевых регистра, причем нулевой выход триггера в каждом регистре соединен с нулевым входом предшествуюгцего триггера; нулевой выход каждого триггера первого регистра соединен с входом соответствующей схемы И-HE первой группы, а выход этой схемы соединен с входами схем И-HE соответствующего столбца матрицы, выходы которых соединены с единичным входом последующего триггера этого регистра; нулевой выход каждого триггера второго регистра соединен с входом соответствующей схемы И-HE второй группы, другой вход котррой соединен с единичным входом предшествующего триггера, а выходс входами схем И-НЕ соответствующей строк и м ат рицы, Я

Бель изобретения — упрошение устройства. для этого в предлагаемом распределителе выходы всех схем И-НЕ каждого столбца матрицы соединены с входами схемы

И-HE первой группы, соответствующей этому столбцу; выход каждой схемы И° HE, кроме последней, первого столбца р матрицы соединен с входом предшествующей схемы И-НЕ того же столбца, а выход последней схемы И-HE — с входом первой схемы этого столбца; вход каждой схемы И-НЕ, кроме последней, последне1в ro столбца матрицы соединен с входом последующей схемы этого столбца, авход последней схемы И-ИŠ— с входом первой схемы этого столбца; выход каждой схемы И-НЕ, кроме первой, в каждой строке

20 матрицы соединен с входом последующей схемы И-НЕ, а выход первой схемы ИНŠ— с соответствующим входом последней схемы И-ИЕ той же строки; вход распределителя Такт" соединен с соотИ ветствуюшими входами схем И-HE мат451074 рицы, выходы которых соединены с выходными шинами распределителя.

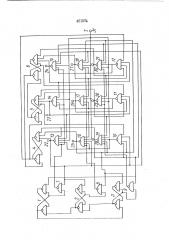

Ца. иртеже изображена схема предлагаемого распределителя. !

Устройство содержит триггеры 1, 2 и 3 управления строками матрицы; триггеры 4, 5 и 6 управления столбцами матрицы; группу схем И-НЕ 7, .8 и 9 уп равления строками матрицы; группу схем И-НЕ 10, 11 и 12 управления столбцами

1 матрицы; матрицу схем И-НЕ 13-21; выходные шины 22-30 матрицы; шину 31

Такта

На чертеже приведена схема распределителя с числом разрядов в каждом реги-: стре, равном 3.-Каждый элемент матрицы ,производит сдвиг единицы в первом реги1

t итре на один разряд, а набор элементов одной строки матрицы обеспечивает циклический сдвиг единицы в первом регистре, крайний левый элемент И-НЕ каждой строки матрицы производит, кроме того, сдвиг еди ницы на один разряд во втором регистре. В начальный момент времени триггеры 1 и 6 устанавливаются в положение единица". Остальные триггеры находятся в состоянии нуль". Так как в начальный момент времени входной сигналЧ, подаваемый на шину 31, отсутствует, т.,е, равен,, логическому нулю,. на выходе схем И-НЕ

13-2 1 будет логическая единица, следо- вательно, на выходе схем И HE.8- 12 бу- дет логический нуль, а на выходе схемы

И-HE 7 и ll — логическая единица. Сприходом входного сигнала на выходе схемы

И-HE 14 появляется сигнал, соответствующий логическому нулю, который устанавливает триггер 5 в состояние "единица", т. е. на нулевом выходе триггера 5 появляется сигна, равный логическому нулю, 1 который устанавливает триггер 6 в состоя-, ние нуль . Так как выход схемы И-НЕ

14, кроме того, заведен на схемы И-НЕ

13 и 11, то на выходах схем И-HE 13 и 1 1 логический нуль не появится, хотя триггеры 5 и 6 изменили свое состояние.

Действительно, сигнал со схемы И=НЕ 14 поступает на схемы И-НЕ 13 и 11 раньше, чем изменение значения сигналов с выходов триггеров 5 и 6, Таким образом, 1 на шине 23 будет сигнал, который может быть направлен по одной изп выходных шин. После окончания действия входного сигнала на выходах схем И-HE 13-21 снова будет логическая единица, на выхо.дах схем И-НЕ 8, 9, 11 и 12 - логиче:.ский нуль, а на выходах схем И-НЕ 7 и

10 - логическая единица. С приходом сле дующего входного сигнала Г логический нуль появляется на выходе схемы И-НЕ . 13, который устанавливает триггеры 2 и

5 4 в положение единица" и который с выхода шины 22 может быть направлен по

:следующей из т . выходних,шин, при атом триггеры l. и 5 сигналами,с нулевых вы ходов триггеров 2 и. 4. устанавливаются

Я в состояние нуль . Наличие связей с вы,хода схемы И-HE 13 на входы схемы И, НЕ 7, 16, 10, 15.и 18 препятствует по-! явлению. на выходах этих схем логическо; го нуля. С приходом следующего входного

15 сигнала логический нуль появляется на выходе схемы И-НЕ 18, который с вых да шины 27 может быть направлен по следующей изб выходных шин и который устанавливает триггер 6 в состояние еди20. ница". Нулевой выход триггера 6 устанавливает триггер 4 в состояние нуль". С приходом следующего входного сигнала логический нуль появляется на выходе . схемы И-НЕ 17, который с шины26 можа

25 быть распределен по следующей изб выL ходных шин. Аналогичным образом входной сигнал будет распределен по остальным выходным .шинам, при этом за один цикл сдвига единицы в регистре триггеров управ50ления столбцами матрицы единица в регистре

t управления строками матрицы сдвигается, на один разряд.

В общем случае число регистров уст ройства и число разрядов в каждом регистре может быть любым, при этом не обязательно, чтобы число разрядов в одном регистре равнялось числу разрядов в другом регист,е.

Предмет изобретения

Распределитель импульсов, содержащий матрицу схем И-НЕ, две группы схем ИНЕ и два кольцевых регистра, причем нулевой выход триггера в каждом регистре соединен с нулевым входом предшествую щего триггера; нулевой выход каждого 50 триггера первого регистра соединен с

:входом. соответствующей схемы И-HL nepвой группы, а выход этой схемы соединен с входами схем И-НЕ соответствующего столбца матрицы, выходы которых соедине. ны с единичным входом последующего

55:1, i триггера этого регистра; нулевой выход каждого триггера второго регистра соединен с входом соответствующей схемы И-НЕ

* 81074

5. .6 второй группы, другой вход которой соеди-, каждой схемы И-НЕ, кроме последней, понен с единичным входом предшествующего следнего столбца матрицы соединен с вхо триггера, а выход с входами схем И-НЕ дом последующей схемы этого столбца, а соответствующей строки матрицы, о т - .. вход последней схемы И-НЕ - с входом л и ч а ю шийся тем, что, с целью 5I первой схемы этого столбца; выход кажупрощения распределителя, выходы всех,дой схемы И-НЕ, кроме первой, в к йщой схем И-БЕ каждого, столбца матрицы соеди- строке матрицы соединен с входом посленены с входами схем И-НЕ первой группы, дующей схемы И-НЕ, а выход первой схесоответствующей этому столбцу; выход,мы И-HE — с соответствующим входом каждой схемы И-НЕ, кроме последней,пер- 10 последней схемы И-НЕ той же строки; вого столбца матрицы соединен с входом, вход распределителя Такт соединен ссо предшествующей схемы И-НЕ того же стол@- ответствующими входами схем И-НЕ матI

:ца, а выход последней схемы И-НЕ - с рицы, выходы которых соединены с выходвходом первой схемы этого столбца, вход — ными шинами распределителя.