Селектор импульсов по длительности

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистииескик

Республик (11) 45 IIS6 (61) Зависимое от авт. свидетельства— (22) Заявлено I4,04 72 (21)I773I09/2 с присоединением заявки Й— (32) Приоритет—

Опубликовано25, IQ,74 þëëåòåíü K 43

Дата опубликования описанияЕ5о Е2е74 (51} h1. Кл.

Н ОЗК 5/20

Государственный коиетет

Совете Министров СССР оо деяаи изобретений и открытий (5 ) УД1 62I 374. . 332(088, 8) Ю.Н. Ерофеев о (72) Автор изобретения

ВПТБ е ф 1ьооее фЯф (71) Заявитель

Изобретение относится к телевизионной технике, а именно к селекции видеоимпульсов заданной длительности из совокупности разнороддых импульсных сигналов ° s известны селекторы, содержащие генератор тактовых имйульсов, схемы яыделения и линии задерллй. днако в известных селекторах возможно ложное срабатывание от то импульсов меньшей длительности, период следования которых равен заданной длительности селектируемого сигнала °

Целью изобретения является полу- т5 чение широкого диапазона изменения селектируемой длительности входных сигналов и исключение ложного срабатывания селектора при длительности сигнала, кратной длительности заданного.

Аля этого выход генератора тактовых импульсов соединен с одним из входов первой схемы совпадения, второй вход которой подключен к входной клемме селектора и через последовательно соединенные дифференцирующую цепь, ограничитель и уаилитель - к входу сброс" счетчика, счетный вход которого соединен с выходом первой схемы совпадения, а выходы счетчика подключены к входам двух деп1ифраторов, причем выход первого дешифратора соединен с входом триггера, выход которого соединен с первым входом схемы сов1.адения на три входа, на второй вход которой подан сигнал другого триггера по входу связанного с вгорым дени рагором, а на грехни вход посхупаех импульс, с4врмированнын из заднего фронта входного сигнала.

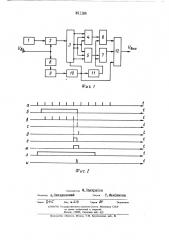

Изобретение пояснено чертежами.

На фиг. Е приведена функциональная блок-схема селектора; на фиг.2временные диаграммы. селектор импульсов по длительности содержит генератор 1 выход которого соединен с первым входом схемы совпадения /клапана/ а, на (54) СИПНтОР ааПЬСОВ ПО РИтЯЬНОСтИ

45П86

3 второй вход схемы 2 поступают входные импульсы. выход схемы 2 соединен со счетчиком импульсов 3. Выходы счетчика 3 соединены с дешифраторами 4 и 5, которые срабатывают при воздействии и -го и (й + )-го сигнала на входе счетчика /например счетчик выполнен на типовых потенциальных триггерах, дешифратор 4 выделяет пятый имйульс, а дешифратор Ь вЂ” такт, соответствующий шестому счетному импульсу/.

Выход дешифратора 4 соединен с вхоом триггера б, выход дешифратора — с входом триггера !. Каждый из 1ü триггеров б и 7 включен по схеме с раздельным запуском. Кроме схемы совпадения 2 входной импульс паступает также на вход дифференцирующей цепи 8, служащей для выделения 20 импульса, соответствующего заднему ронту входного сигнала. выход диференцирующей цепи 8 связан с входом ограничителя 9, служащего для выделения импульса, соответствующе- ы го заднему фронту входного сигнала .

Выход ограничителя 9 связан с усилителем мощности IO который только усиливает полученные импульсы без изменения их временного по- 3р ложения. выход усилителя 10 связан с входом "сброс счетчика 3 входом задерживающего устройства II, входом схемы совпадения L2 .

Задерживающее устроиство Il должно обеспечить сдвиг импульсов, немного превышающии время опрокидывания выбранных триггеров. В качестве задерживающего устройства П может бить использована линия за- 4о держки с небольшим временем задержки (О, — 0,2 мксек} или двойной инвертор.

Выход задеркивающего устройства

Псоеданен с вторыми раздельными вхо- 4 дами триггеров 6 и 7. Выходы триггеров

6, 7 соединены о входами схемы совпа- . дения 12, имеющей, таким образом, три входа; Выходной импульс снимается с выхода схемы совпадения 2

Селектор импульсов работает следующим образом.

Входные импульсы (см.фиг . 2, б) тактовые импульсы генератора Х см.фиг. 2, a) поступают на входы схемы совпадения 2. Сигнал на выходе этой схемы будет проходить только в течение времени действия входного сигнала ем.фиг . 2, в) .

Те тактовые импульсы, которйе ррой° ° ° т аа выход схемы совпадения < см.фиг . 2, в) попадут на вход счет чика 3.

4 период тактовых импульсов и число тактов, которые может отсчитать счетчик, определяют точность работы селектора.

II р и м е р. Длительность импульса соответствует заданной, если она лежит в пределах между пятым и шестым тактами счетчика (B общем случае между и -ым и (и +К) ым}.

На фиг . 2 приведен именно такой случай, когда длительность импульса дежйт в зоне селекции.

1 ри работе счетчика 3 на пятый такт вырабатывается импульс дешифратора 4. ередний фронт этого импульса (см .фиг . 2, е) запускает триггер б. На выходе триггера б также появляется высокий уровень выходного напряжения (см.фиг . 2,ж) триггера 7 используется противоположный выход по сравнению с триггером 6), почему сигнал на

ыходе триггера 7 уже существует.

1оэтому на первые два входа схемы совпадения Е2 поступает импульс, сформированный из заднего фронуа входного сигнала (см.фиг . d, r} . поскольку на всех трех входах схемы совпадения Т2 на время действия импульса (см.фиг., r) будет высокий потенциал, появляется выходной импульс на вйходе схемы совпадения 12, говорящии о том, чтс длительность входного сигнала соответствует заданной.

Йосле того как анализ сигнала закончится, произойдет сброс счетчика 3 и триггеров ь, 7 . I риггера счетчика 3 сбрасываются задним ронтом входного .сигнала см .фиг .,, г); триггера О, 7 сбрасываются с небольшой задержкой, обеспечива° 2 мой задерживающим устройством 1 см .фиг . 2, д) . осле сброса селектор готов к анализу следующего поступающего импульса. сли длительность входного импульса будет меньше заданной, то счетчик 3 сбросится задним фронтом сигнала раньше чем досчитает до пятого такта. Сигнал на выходе дешифратора 4 йе появится, триггер б не запустится и на первом входе схемы совпадения 12 высокий потенциал за время анализа этого импулься не появится. Отклика на выходе селектора на указанный импульс не будет. лсли длительность импульса больше заданной, то после счета на пятом.такте и срабатывания дешкфратора 4 и триггера 6 счетчик З отсчитает и шестой такт, Ops этом

45II86

5 сработает дешифратор 5. Он запустит триггер 7 и высокий потенциал на выходе триггера 7 сменится на низкий.

На втором входе схемы совпадения I2 к моменту прихода сигнала, сформированного из заднего фронта входного импульса, не будет высокого потенциала. Отклика на выходе схемы совпадейия I2 не будет и в этом случае.

З каждом случае после анализа входного импульса селектор вновь приводится в готовность путем сброса триггеров б, 7 и счетчика 3.

На выходе селектора импульсы появляются только в том случае, если длительность входного сигйала соответствует заданной. изменять длительность селектируемого импульса можно путем перестройки периода повторения импульсов тактового генератора 1 . Ручку регулировки периода колебаний генератора 1 можно проградуировать непосредственно в длительностях селектируемых импульсов. тносительная точность работы селектора во всем диапазоне перестройки сохраняется. сходя из принципа построения, предложенный селектор может быть реализован на типовых логических компонентах в интегрально-схемном исполнении.

ПРИМЕТ ИЗОБРЕТЕНИЯ

Селектор импульсов по длитель5

1о

2О

35 б ности, состоящий из генератора тактовых импульсов с регулируемым периодом повторения, схемы совпадения, счетчика, двух дешифраторов и формирователя импульсов по времени совпадаищих с задави фронтом входных сигналов, о т л и ч аю шийся тем, что, с целью получения широкого диапазона изменения селектируемой длительности входных сигналов, и исключения ложного срабатывания селектора при длительностях сигнала, кратных длительности заданного, выход генератора соединеч с одйим из входов первой схемы совпадения, второй вход которой подключен к входной клемме селектора и через последовательно соединенные дифференцирувщую цепь ограничитель и усилительк входу сброс" счетчика, счетный вход которого соединен с выходом первой схемы совпадения, а выходы начетчика подключены к входам двухдешифраторов, один из которых срабатывает при воздействии п-го сигнала на входе, а второи — при воздействии (й + )-го сигнала, выход первого дешифратора соедйнен с входом триггера, выход которого соединен с первым входом схемы совпадения на три входа, на второй вход которой подан сигйал другого триггера, по входу связанного с вторым дешифратором, а на третий вход поступает импульс, суормированный из заднего фройта входного сигнала. алых составитель М»ПЙнкДВтов

Редактор Аа ВИН >КШЗСКИЙ- Т. Максимова

Заказ Изд. NI б/ф Тираж gd

Подписное

ЦНИИПИ Государстаениого комитета Совета Министров СССР по делам изобретений и открытий

Москва, I 13035, Раушская наб., 4/

Предприятие «Патент», Москва, Г-59, Бережковская наб., 24