Логический элемент

Иллюстрации

Показать всеРеферат

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВЙДЕТЕДЬСТВУ

Союз Советских

Социалистиыесмих Республик (11) 45IE95 (61) Зависимое от авт. свидетельства (22) Заявлено19, 07. 72 (21) 18 12535/2 (51) М. Кл.

Н ОЗк I9/08 с присоединением заявки

Государстаенный иоиитет

Совета Мннистрао СССР оо делаи изобретений н открытий (32) Приоритет (53) УДк 62I.374 (088.8) Опубликовано25, |g,74юллетень № 43

Дата опубликования описания 5,g2,74

BAT 5

Ф!ЕД 3huniqkcPTjg

В.И.Лебедев (72) Автор изобретения (71) заявитель @ сксвскии ОРДена ТРУДОВОГО КРаснОГО BHBMBHE инженерно-физический институт

Л(Н ИЧЕСБИЙ 3КЕМЕНТ (54) 1

Изобретение относится к вычис- лительной технике и цифровой автоматике, в которых подобные логические элементы применяются в арифметических и управляющих устройствах

ЦВМ, устройствах преобразования аналог-код, различных коммутаторах, выполняющих свои функции при относительно низких логических сигналах

В известных логических элементах используют токовые ключи на транзисторах со связанными эмиттерами, переключение которых осуществляется при помощи тактовых импульсов при подаче на вход сигналов.

Однако использование токовых ключей обусловливает большое число источников питания, большую потребляемую мощностьи нйзкую тепловую стабильность, а также сложность элемента.

Целью изобретения является уменьшение потребляемой мощности и упрощение элемента. для этого в элементе база первого логического транзистора соединена с коллекторами остальных логических транзисторов.

s Изобретение пояснено чертежами.

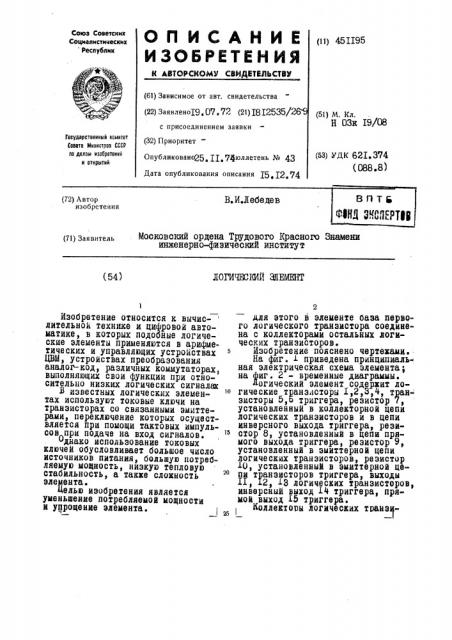

На фиг. приведена принципиаль ная электрическая схема элемента; на фиг . 2 - временные диаграммы. логический элемент содержит ло1О ГИЧЕСКИЕ тПаНЗл1СтсрЫ Х,2,З,М, траНзисторы 5,Ь триггера, резистор 7, установлейный в коллекторной цепй логических транзисторов и в цепи инверсного выхода триггера, резистор 8, установленный в цейи прямого вйхода триггера, резистор 9, установленный в эмиттерной цепи логических транзисторов, резистор

Ц), установленный в эмиттерной цепи транзисторов триггера, выходы

lI, 12, la логических транзисторов, инверсйый выход 1М триггера, прямой выход И триггера.

Иоллелхооы логических гоеыел45П95

3 сторов 2 2, 3 объединены с коллектором транзйстора э триггера и к точке объединения подключен резистор 7. Коллектор первого логического транзистора 4 объединен с коллектором транзистора о и базой транзистора 5 и к точке объединения подключен резистор 8. К резисторам 9 и 10, установленным в эмиттерных цейях, подключаются исочники импульсного питания б и

7, напряжения которых равны Ы . и

E . соответственно.

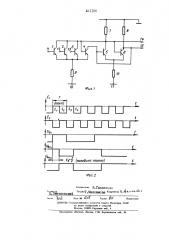

Логический элемент работает следующим образом.

До подачи входного сигнала, когда на входах l, 2, 1Ы держится низкик уровень трайзисторы l, 2, 3 закрыты и ток зы нипульснотii !1Мrats от источника l6 протекает через транз,: стор 4 и резистор 8, создавая низкое напряжение на базе транзистора 5.

Носле сиены фаз напряжении и 2 импульсного питания ток потечет через открытый транзистор б, поддерживая низкий уровень, принятый за логическир1 нуль на йрямом выходе триггера и, следовательно, поддерживая высокйй уровень, прийятый за логическую единицу, йа инверсном выходе. после включения входного сигнала

Ум = на один из входов Х1, 2, 3 в момент, когда фаза, = О, выходное найряжение поддерживается на прежнем уровне a . течение половины такта.

Ы момент 6 ток будет протекать через открытый транзистор (или

3) и резистор 7 (как в обычном токо воы ключе, иыеющеы регенеративную обратную связь) . Следовательно, получим на выходе Т4 Ыык, = О, йа выходе l5 xi = 1. 3 ыоыейт t>, когда L4 = О, включается напряжение Fg, обесйечивая протекание тока через резистор 7 и запоминание инi ормации, поданнои на вход . i îE в этом случае будет протекать через транзистор, а не б в связи с теы, что напряжейие на базе транзистора б сохраняется на низком уровне . Такое запоминание низкого уровня объясняется тем, что емкость перехода коллектор=база транзистора 5 не успевает перезарядиться при мене фаз. Аналогичной памятью обла. дает и емкость перехода коллекторбаза транзистора ь.

Влагодаря двойнои емкостной пе.мяти уменьшается влияние разброса параметров и снижаются требования K

5О

Логический элемент, содержащий триггер на транзисторах со связанныыи эыиттерами, соединенными с шинои иыпульсного питания, и логические транзисторы со связанными эыиттерами, подключенными к другой шине импульсного питания, причем коллектор первого логического транзистора соединен с базой одного из транзисторов триггера, у которого коллектор соединен с коллекторами остальных логических транзисторов, подключенных базами к входным шинам, отличающийся тем, что, с целью уменьшения потребляемй мощйости и упрощения, s нем база первого логического транзистора соединена с коллектораыи остальных логических транзисторов.

4 фронтам импульсов питания. осле момента 1 состояние логи. ческого нуля на прямом выходе триггера может храниться неограниченно долго: благодаря чередованию фаз

5 напряжений, Ж:у ток в этом случае протекает через резистор 8. ерез резистор 7 протекает при этом относильно малый ток базы, поэтому на инверсном вйходе храйится также

10 неограниченно долго состояние логической единицы (и наоборот) .

Элемент разработан специально для работы от импульсных источников питания и теряет работоспособ15 ность при замене источников импульсного напряжения Тб, 7 источником постоянного тока.

Из рассмотрения принципа действия следует, что элемент является

2о логическим йолутактовым элементом, создающим задержку сигнала на половину периода, т .9. выполняющим функцию синхронйого полутактового

Я=триггера наряду с функцией "ИЛИ25 НЕ-ИЛИ".

Алд создания тактового синхронного Д= риггера, т.е. для получения аадержки на полныи период, необходимо иметь два полутактовйх

Зо элемента: инверсный выход первого, питающегося от напряжений 1>, Е, долкен Сыть включен на вход зторого элеыента с инверсным фазовым питанием ф, Е ).

Предложеннй элемент имеет логические входы и обеспечивает возможность выполнения логической функции

"МЛИ-НЕ-ИЛ11", он характеризуется логической гйбкостью, имеет прямой

4о и инверсный выходы, сравнительно низка потребляемая мощность .

ПРКдЫЛТ ИЗОБРЛЕНЫЯ

17 р Д Изд. hh к./ Тираж f il

Подписное

Ц11ИИПИ Государственного комитета Совета Министров СССР по делам изобретений н открытый

Москва, 113035, Раушская наб., 4

Заказ

Предприятие «Патент», Москва, Г-59, Бережковская наб. ° 24

Составитель Д ццщс1 дП

Рega op Техре T MaZCmMOaa Корректор Ц, А «- н" n " Ы

А. аиньковский