Счетчик импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАЙ И Е

ИЗОБРЕТЕН ИЯ

И АВТОРСКОМУ СВИДДТИЛЬСТВУ (») 45II98

Сотоз Советск

Соцееалнстее«еснеа йевсетубанн (61) Зависимое от авт. свидетельства(22) Заявлено 08.09.72 (21) I826I88/

/26-9 с присоединением заявки(5l) M Кл.

Н 03к 2I/34 (32) ПриоритетОпубликованс25. П .74Бюллетень № 43 (45р Дата опубликования opia т оондерственный ноннтет

Совете Мнннетров СССР оо делом нвебретеннй н откр«тнй (М) УЛК

62I..374. 32 (088.8) (72) Авторы изобретения

3.0.Вольфовский, И.И.Трофимов и И.К.Хомяков (71) Заявитель (54) СЧЕТЧИК ИМПУЛЬСОВ

Изобретение относится к импуль- сной технике.

Известен счетчик импульсов, содержащий элементарные счетиикй одинаковой разрядности со схемой

QlE на входе, триггер со схемой И и на единичном выходе, элемент задержки и узел контроля нулевого состояния устройства, причем первые входы схем ИЛИ соединены с выходом схемы И, вход которой соединен с шиной входных импульсов контроля, выход переноса каждого элементарного счетчика соединен с вторым входом схемы ИЛИ последующего элементарного счетчика, единичный вход триггера соедийен с шиной контроля .

Йель| изобретения является повышение полнотмисокращения времени контроля и расширение функциональных возможностей устройства.

Для этого оно дополнительно содерзит многовходовув схему ИЛИ, входы которой соединены с выходами

2 переноса элементарных счет йиков, а выход соединен с нулевым входом триггера, выход схемы И соединен с первым входом схемы ИЛИ первого д элементарного счетчика через эле-. мент задержки, шина контроля дополнительно соедйнена с входами установки нуля старших разрядов всех элементарных счетчиков, с входами

<р установки нуля младших разрядов всех элементарных счетчиков, кроме первого, и с входами установки единицы всех остальных разрядов элементарных счетчиков.

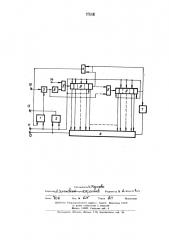

15 На чертеже приведена функционалная блок=схема счетчиков.

Счетчик импульсов содержит триггеры i, 2, схему И 3, многовходовые схемй ИЛИ 1й, 5, многого входовув схему И 6, элементы за-. держки V,B, элементарные счетчики 9 одинаковой разрядности, шину входных импульсов контроля 0, шину контроля I, шину исправно" 2е 5 шину "неисправно I3, вход счетчи45Н ка в режиме работы после окончания проверки 14.

Счетчик работает следующим образом ри поступлении сигнала на ши- s ну 1 триггеры < и 2 устанавливаются в состояние " ", в первом счетчире 9 устанавливается число

Я =2" 1, где п - число разрядов элементарного счетчика, а в осталь- 1О ннх счехчиках w усханавлвваачр число = 2 - -р . хема и открывается и пропускает входные импульсы на входы всех счетчиков 9.

После поступления на шину О числа импульсов, равного 2 1, в первом счетчйке 9 будет зафиксировано число 2", а в остальных счетчиках — число 2 " 2 .

Следующий импульс входной часто- О ты устанавливает все счетчики кроме первого, в состояние 2 а при поступлении импульса с Выхода элемента 8 на выходе первого счетчика 9 формируется импульс переполнения, который вызывает переполнение всех остальных счетчиков 9. В результате все разряды счетчиков устанавливаются в состояние "О". Импульс переполнения с выхода первого счетчика 9 поступает через схему ИЛИ М на нулевой вход триггера . Схема И 3 закрывается, и поступление входных иипульсОВ на ВхОды счетчиков прекрадается. импульс переполнения последнего счетчика задерживается элементом 7 на время Т, где Т - период следования Входных импульсов. Сли все разряды счетчика установлены в состояние "О", то схема б открыта и импульс с вйхода элемента 7 поступает на шину 2 и на нулевой вход триггера 2. сли вследствие неисправности не будет установлен в состояние "<У какой=.либо разряд счетчика 9 ияи триггер I, то сигнал на выходе схемы б не формируется, триггер 2 остается в состоянии " 1 " и с ши8 ны З можно снять сигнал "неисправно".

При формировании ложного импульса переполнения в каком=либо счетчике У триггер будет установлен в состояние "ц", и поступление входных импульсов на входы счетчиков прекращается. следствие этого импульс на выходе схемы И б не фо мируется и триггер .2 остается в состоянии "I

ПРЕДМЕТ И30БРКТЕНИЯ

Счетчик импульсов, содержащий элементарные счетчики одинаковой разрядности со схемой ИЛИ на входе, триггер со схемой М на единичном выходе, элемент задержки и узел контроля нулевого состояния устройства, причем первые входы схем ИЛИ соединены с выходом схемы И, вход которои соединен с шиной входных импульсов контроля, выход переноса каждого элементарного счетчика соединен с вторым входом схемы ИЛИ последующего элементарного счетчика, единичный вход триггера соединен с шиной контроля, отличающийся тем, что, с целью повышения полноты и сокращения времени контроля и расширения функциональных возможностей устройства, оно дополнительно содержит многовходовую схему ИЛИ, входы которой соединены с выходами переноса элементарных счетчиков, а

ВЫХОД СОЕДИНЕН С НУЛЕВЫМ ВХОДОМ триггера, выход схемы И соединен с первым входом схемы ИЛИ первого элементарного счетчика через элемаш задержки, шина контроля дополнительно соединена с входами установки нуля старших разрядов всех элементарных счетчиков, с входами установки нуля младших разрядов всех элементарных счетчиков, кроме первого, и с входами установки еди-. ницы всех остальных разрядов элементарных счетчиков.

Составнтель Ll ° RgUHA иЯ.3инькой ки ч ЮКропачее о

Зак.з $06 1(зд. М бИ Тираж 81/

Подписное

ГГ111Н1П! l Г осударствениого комитета Совета Министров СССР но делан нзобрстеннй н открытий

Москва, 113035, Раушская наб., 4

Преднрнятне Патент>, Москва, Г-59, Ьережковская наб., 24