Универсальный статистический экспрессанализатор

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ „„„„, ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 07. 12. 72 (21) 1856386/18-24 с присоединением заявки ¹â€” (51) М. Кл, 6 06f 15!36

Гасударственный комитет

Совета Министров СССР по делам изобретений и открытий (32) Приоритет—

Опубликовано 30.11.74 Бюллетень № 44

Дата опубликования описания 1 О4 75 (72) Автор изобретения

В. С. 1 ладкий (71) Заявитель

Морской гидрофизический институт АН Украинской ССР (54) УНИВЕРСАЛЬНЫЙ СТАТИСТИЧЕСКИЙ ЭКСПРЕСС-АНАЛИЗАТОР вано для вычисления всех основных характеристик двух случайных nponeccoa )((и .>.1 в реальном масштабе времени: матема|ического ожидания /71 Я дисперх сии ф Я коэффициента взаимной кор-х) реляции Л, автокорреляционной функху пии g ("), взаимокорреляциойной функ- 1р

xx ции g ((,) радиуса корреляции Rk функций распределения р). Особенностью .устройства является его способность, кроме перечисленных характеристик, вычислять также функции спектральной плотности „ (и21 с " 1 l5 и взаимной спектральной плотности Я (@1 хн

Известны универсальные анализаторы> содержащие формирователь, детектор, ий вертор, селектор, блок преобразования, дискриминатор, частотомер Ь генератор импульсов, блок задержки, блок модуляции и блок опорного сигнала.

Однако применение в таких анализаторах обычных цифровых узлов делает их

Изобретение относится к области вычислительной техники и может быть использогромоздкими и дорогими, при использовании аналоговых элементов их частотный. диапа-. зон резко сужается, они имеют невысокую точность и плохо стыкуются с цифровыми

ЭВМ. Кроме того, известные анализаторы требуют запоминания всей входной информации и многократного ее считывания в

>т>процессор, что удорожает анализатор, делает его непригодным для анализа процесса в реальном масштабе времени.

11ель изобретения - повышение быстро действия анализатора без существенного усложиения его схемы.

Это достигается тем, что к второму входу выходного регистра подключен выход блока вычисления радиуса корреляции, а к третьему — выход блока реверсивных счетчиков и входы блока вычисления радиуса корреляции и блока нормализации, выход которого соединен с первым входом второ-, го блока динамической памяти, второй вход которого соединен с выходом блока управления, с первым входом первого блока динамической памяти и с первым входом бло

-ка пакетного умножения, а выход - с вто452000 рым входом олока пакетного умножения, третий вход которого подключен к выходу блока выработки спектрального окна, четвертый — к выходу первого блока динамической памяти, пятый — к выходу блока вероятностного округления, к первому вхо ду первого" блока динамической памяти и к входу блока вычисления математических ожиданий, выход которого через блок умно» жения соединен с первым входом блока реверсивных счетчиков, второй вход которого подключен к выходу блока пакетного умножения, второй вход первого блока дина мической памяти соединен с выходом блока выработки косинусов, 15

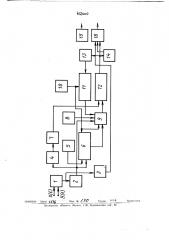

На чертеже показана блок-схема анаиизатора, где 1 — преобразователь аналог-код, 2 — блок вероятностного округления, 3 — ))) блок вычисления функций распределения, 4блок вычисления математических ожиданий,, 5 — блок выработки косинусов, 6 — первый блок динамической памяти, 7 — блок умножения, 8 — блок выработки спектрального окна, 9 - блок пакетного умножения, 10— блок управления, 11 — второй блок динамической памяти, 12 — блок реверсивных счетчиков, 13 - блок норма))изации, 14 — блок вычисления радиуса корреляции, 15 — пре- ЗО образователь код-аналог и 16 — выходной регистр.

Выход преобразователя аналог-код соединен с входами блоков 2 и 3. Выход блока

3 подключен к первому входу выходного ре- gg гистра 16. Выход блока 2 связан с первым входом первого блока 6 динамической намяти с четвертым входом блока 9 и с входом блока 4. Выход блока 4 через блок 7 умножения подключен к первому входу блока 4{)

12 реверсивных счетчиков, второй вход которого соединен с выходом блока 9 пакетного. умножения, а выход — с входом блока

14 вычисления радиуса корреляции, с третьим входом выходного регистра 16 и через -45 блок 13 нормализации - с первым входом второго блока 11 динамической памяти, второй вход которого подключен к выходу блока 10 управления, к третьему входу первого блока динамической памяти и к 60 второму входу блока 9 пакетного умножения, третий вход которого соединен с выходом блока 8 выработки спектрального окна, а пятый — с выходом первого блока динами- ческой памяти, второй вход которого под- 55 ключен к выходу блока 5 выработки ко(инусов. Выход выходного регистра 1 6 со единен с входом преобразователя 15 код аналог.

Анализатор работает следующим образом.

В блоке 1 аналоговая информация преобразуется в цифровую. Если на вход поступает цифровая информация, она минует ,блок 1 и подается непосредственно в блоки 2 и 3, В блоке 2 многоразрядные числа (10-12 двоичных разрядов) округляются вероятностным способом до 4-7-разрядных и поступает в блоки 4 и 6. В блоке 4 вычисляются ff и Щ которые за)с тем перемножаются в блоке 7. Если идет обработка только одной функции ЯЦ, в блоке 4 вычисляются два значения Щ х которые в блоке 7 возводятся в квадрат.

В блок 6 первоначально заводится И.первых чисе)) ряда g®, затем в блоке 9 все Щ чисел умножаются на )Л -е число ряда gg), либо ряда)(Я} в зависимости от того, что отыскивается авто- или взаимнокорреляиионные харснстеристики процесса.

Результаты перемножения заносятся в ревер)с))вные счет шки блока 12..

В следуюц)ий момент в блок 6 записываетсч,новое число обрабатываемого ряда, при этом первое число ряда из блока 6 вы4одится и далее в обработке уже не участвует. Процесс у) п)ожения повторяется (теперь уже второго числа ряда на все чисел, начиная с второго), результат 1 также фиксируется в блоке 12. Описанные операции повторяются до поступлен))я в блок

6 последнего числа ряда, На этом завершается вычисле)ше первых и вторых моментов

;«Лнлесса ((Ц илн )(у(ф Выниеление:eevepItIaeIcII в момент поступления последнего, числа ряда, и таким образом обработка информации при этом может осуществляться в реальном масштабе времени при скорости ввода чисел со скоростью, равнои максимальной скорости пере)с)почел))я используемых элементов. Цинна обрабатываемых рядов может изменяться от 64 и теоретически до сколь угодно большой величины, однако практически этот диапазон лежит в пределах от 256 до 16512, Если необходима псиная статистическая сб

Ф работка информации, начинаются второй и третий этапы вычисления, во время которых перекрываются входные каналы. В течение второго этапа в блоке 7 перемножа2) ются fQ, и Щ (или вычисляются/Д ) х Х и полу))енное значение вычитается из содер жимого в счетчиках блока 12, при этом

452000

Универсальный статистический экспрессанализатор, содержащий блок вычисления математических ожиданий, блок выработки косинусов, первый и, второй блоки динами ческой памяти, блок умножения, блок выработки спектрального окна, блок пакетного умножения, блок управления, блок реверсивных счетчиков, блок нормализации, блок вычисления . радиуса корреляции, преобразователь аналог-код, выход которого соединен с входами блока вероятностного окру . пения и блока вычислелпи функций распределения, выход которого подключен к первол у входу выходного регистра, выход ко- торого соединнн с входом преобразователя, код-аналог, отличающийся тем, что, с целью повышения быстродействия анализатора, к второму входу выходного регистра подключен выход блока вычисления радиуса корре иш и, а к третьему— выход блока реверспвных счетчиков и входы блока вычислеш1я радиуса корреляции и блока нормализации, выход которого соединен с первыл| входом второго блока динамической памяти второй вход которого

30 соединен с выходом блока управпения, с третьим входом первого блока динал1ической памяти ц с первым входом блока пакетного умножении, а выход — с вторым входом блока пакетного улшожеши, третий

35 вход которого подключен к выходу блока выработки спектрального окна, четвертый— к выходу первого блока динамической памя ги, пятый — к выходу блока вероятностного ркругления, к первому входу первого блока

4р динамической памяти и к второму блоку вычислеши математических ожиданий, выход которого через блок умножения соединен с первым входом блока реверсивных счет иков, второй вход которого подключен к выхо4ч ду блока пакетного умножения, второй вход первого блока динамической памяти соединен с выходом блока выработки косинусов. осуществляется центрирование корреляционной функции. На третьем этапе вычисляется спектральная функция. При этом из блока

1 2 значение корреляционной функции переписывается в блок 11 динамической памяти через блок нормализации, в котором коррелиционная функция приводится к интервалу (0,1). Одновременно в блоке 14 вычисляется радиус корреляции (. . ). Счетчики блока 12 обнуляются. B блоке 5 вырабаты\ ваются первые Щ значений С.Оба, = Я. т «= 1 tn и заносятся в блок 6, В блоке 8 вырабатывается первое значение функции спектрального окна (например, для фильтра Хеннинга оно составляет (+ СОЙс " j"-g . Значение К0, взятое из блока 11, и значение W перемнажаются в блоке 9 между собой, а также сразу на все значения СО С (=, 2 -. 6

Результат заносится.в счетчики блока 1 2.

B следующий момент блок 5 вырабатывает новые Щ. значений Gg52 J при /М .

Одновременно в блоке 8 вырабатывается очередное значение функции спектрального окна (14СЩ, С ), которое умножается в блоке 9 на.Я и на /ц новых значений

1 j,, которые содержатся в блоке 6. Результат также заносится в tQ. счетчиков блока 12. Далее процесс повторяется аналогично описанному с той лишь

Ф б разницей, что — на J -м шаге, / =1 2,... РИ блок 5 вырабатывает новые + значений

COQUE. °, а блок 8 -е значение функции спектрального окна и из блока 11 в блок пакетного умножения поступает -е значение корреляционной функции >4 .

На Щ -м шаге процесс вычисления спектральной функции завершается, затем все вычисленные значения из блоков 4., 11

12 поочередно считываются в выходной регистр для цифропечати, ввода в ЭВМ, а также на преобразователь код-ана юг для осциллографирования. После этого:входные цепи анализатора открываются и он вновь готов для статической обработки информации.

Предмет изобретения