Устройство для защиты памяти

Иллюстрации

Показать всеРеферат

(йсгОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 452036 (61) Зависимое от авт. свидетельства (22) Заявлено 17.07.73 (21) 1945462/18-24 (51) М. Кл. 9 11с

29/00 с присоединением заявки М—

Государствеииый комитет

Совета Министров СССР по делам иэооретений и открытий (32) Приоритет—

Опубликовано 30.11.74 Бюллетень № 44

Дата опубликования описания 29.О3.75 (53) УДК 681.327. .6 (088.8) (72) Авторы изобретения

В. М. Долкарт, Г. Х. Новик, В. Н. Степанов, Ю. М. Евдолюк, М. М. Каневский и И. P. Крамфус (71) Заявитель (54} УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известно устройство для зашиты памяти, содержащее регистр защиты, адресный регистр и регистр перемещения программ, 5 подключенные к выходам операционного блока, один из входов которого соединен с блоком управления выборкой, и триггер обращения в защищенную область памяти.

Предлагаемое устройство отличается от известного тем, что оно содержит схемы

И IH" по количеству разрядов регистра перемещения программ и две группы схем

"И", одни входы которых подключены ксоответствующим выходам регистра зашиты, другие — к выходам адресного регистра, первые входы схем "ИЛИ соединены свыходами регистра перемещения программ, вторые — с выходами схем И" первой группы, а выходы — со входами блока ут 20 равления выборкой, выходы схем "И" второй группы через введенную в устройство дополнительную схему "ИЛИ" подключены ко входу триггера, выход которого соеди- нен с другим входом операционного блока..

25 Эти отличия позволяют упростить устройство.

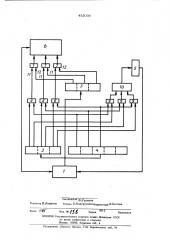

На чертеже изображена блок-схема устройства для защиты памяти.

Устройство содержит операционный блок

1, к которому подключены регистр защиты 2, регистр перемещения программ 3, и адресный регистр 4, триггер 5 обращения в защищенную область памяти, первую группу схем И 6, схемы ИЛИ 7 по количеству разрядов регистра 3, блок управления выборкой Р, вторую группу схем

"И S, дополнительную схему ИЛИ 10.

Одни входы схем И 6 и 9 подключены к соответствующим выходам регистра 2, другие — к выходам регистра 4, Выходы схем И" 6 соединены с первыми входами

11 схем ИЛИ 7, вторые входы 12 которых подсоединены к выходам регистра 3, а выходы — ко входам блока 8. Выходы схем "И 9 через схему ИЛИ 10 подключены ко входу Фриггера 5, выход которого соединен со входом операционного блока 1.

452036

Устройство работает следующим образом.

Перед пуском программ пользователя операционньгй блок 1 устанавливает в первоначальное состояние регистр защиты 2 и 5 регистр 3. Регистр защиты 2 определяет объем памяти, отведенной программам пользователя. Число "единиц в регистре зашиты 2 определяет, какое количество старших разрядов адреса в программах 10 пользователя должно быть нулями (защищено от пользователя) и таким образом, определяет область памяти, отведенную пользо вате лю.

Например, если два старших разряда регистра защиты 3 установлены в "1, то это означает, что программам пользователя отведена четверть памяти и используемые ими адреса, которые устанавливаются в адресном регистре 4, должны иметь в двух старших разрядах "нули".

Если в защищенных разрядах адресного регистра 4 появится "единица", то обращение к этой ячейке памяти блокируется и устанавливается триггер 5.

Блокировка обращения в запрещенную область памяти осуществляется с помощью схем "И" 6, которые передают на входы схем "ИЛИ 7 информацию из старших разрядов адресного регистра 4 только в том случае, если соответствующий разряд регистра защиты 2 установлен в О», Адрес с выходов схем ИЛИ" 7 поступает на вход блока управления выборкой

8, осуществляющего связь с оперативной памятью. Синхронизацию работы блока управления выборкой 8 осуществляет операционный блок 1.

Если адресный регистр 4 имеет 1" в разряде, защищенном в регистре защиты 2, соответствующая схема "И 9 через схему ИЛИ 10 устанавливает триггер 5.

Таким образом, изменяя информацию в тех разрядах регистра 3, которые соотвеч ствуют разрядам защиты регистра 2, операционный блок 1 может,.перемещать программы пользователя в памяти.

Предмет изобретения

Устройство для защиты памяти, содержащее регистр защиты, адресный регистр и регистр перемещения программ, подключенные к выходам операционного блока, один из входов которого соединен с блоком управления выборкой, и триггер обращения в защищенную область памяти, о тл и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит схемы

"ИЛИ по количеству разрядов регистра перемещения программ и две группы схем

И, одни входы которых подключены к соответствующим выходам регистра защиты, другие — к выходам адресного регистра, первые входы схем ИЛИ соединены с выходами регистра перемещения программ, вторые - с выходами схем И" первой группы, а выходы «со входами блока управления выборкой, выходы схем "И второй группы через введенную в устройство дополнительную схему ИЛИ" подключены ко входу триггера, выход которого соединен с другим входом операционного блока.

452036

Изд. М Тираж

Заказ

Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР ло делам изобретений и открытий

Москва, 113035, Рауц ская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская иаб., 24

Составитель В Рудакоа

Редактор В.Левитов Техред E.Ïoäóðóøèíà Корректоры Л.Котова