Запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (11) 452037 (61) Зависимое от авт. свидетельства— (22) Заявлено 23.02. 73 (21) 1890200/18-24 (51) М. K>. G 1 lc

29/00 с присоединением заявки No

Государственный комитет

Совета Миниотров СССР во делам изобретений и открытий (32) Приоритет

Опубликовано 30. 11.74 Бюллетень Ке 44

Дата опубликования описания

29.О3.75 (53) УДК 681.327. .6(088.8) (72) Авторы изобретения

К. Г. Самофалов, В. И. Корнейчук, А. В. Городний и А. И. Небукин

Киевскии ордена Ленина политехнический институт им.50-летия

Великой Октябрьской социалистической революции (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОНОМНЫМ

КОНТРОЛЕМ

Изобретение относится к области запоминающих устройств.

Известно запоминающее устройство с автономным контролем, содержащее регистр адреса, подключенный к накопителям, подсоединенным к регистру силы корректирующего кода и регистру кодового слова, блоки кодирования и декодирования, подключенные к регистру силы корректирующего кода и к одному входу схемы сравнения, другой вход которой подсоединен к выходу схемы определения кратности отказа, блоки схем ИЛИ, выходы которых подключены к входам одного из накопителей и блока декодирования соответственно, и блок управления.

Недостатком известного устройства является большое количество оборудования.

Предлагаемое устройство отличается от известного тем, что оно содержит блоки схем "И и триггер, входы которого подключены к выходам блока декодирования и блока управления, а выходы — к управляющим входам первого и второго блоков схем

И", информационные входы которых соединены с прямым и инверсным выходами

2 регистра кодового слова, а выходы — с входами первого блока схем ИЛИ, информационные входы третьего и четвертого блоков схем И подключены к одному выходу блока декодирования и к инверсному выходу регистра кодового слова, выходы — к выходной шине устройства и к одному из входов второго блока схем "ИЛИ, а вход схемы определения кратности отказа подсоединен к другому выходу блока декодирования.

Это позволяет упростить устройство и повысить надежность его работы.

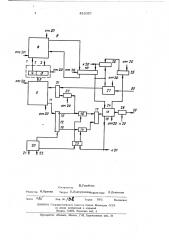

На чертеже изображена блок-схема предложенного устройства.

Устройство содержит регистр адреса 1, имеющий информационный вход 2. Регистр

1 состоит из регистра 3 номера ячейки и регистра 4 номера страницы. Выход 5 регистра 1 соединен с накопителем 6, а выход 7 регистра 4 — с накопителем 8.

Накопитель 6 имеет страничную организацию и обладает емкостью р страниц.

Емкость накопителя 8 определяется количеством страниц накопителя 6 и составляет )ячеек.

452037 ветственно.

Выход 24 блока 18 связан с входом схемы 25 определения кратности отказа, выход которой соединен с одним входом схемы сравнения 26. Выход схемы 26 связан с блоком 20 и с другим входом регистра 10, выход которого соединен с другим входом схемы 26 и с входами блока 18 и блока кодирования 27. 30

Один из выходов блока 18 подключен к информационному входу третьего блока

"И 28, выход которого подсоединен к выходной шине 29.

Входная шина 30 устройства соединена с информационным входом блока 27. Кодовый выход блока 27 связан с одним входом второго блока схем ИЛИ" 31, другой вход которого подключен к выходу четвертого блока схем "И" 32, информационный 40 вход которого подключен к инверсному выходу 15 регистра 12. Выход блока 31 связан с входом накопителя 6. Выход блока 20 подключен к другому входу триг- гера 23.

Устройство работает следуюшим образом.

Соответствуюшая } и (1= J — P ) странице накопителя%,-я ячейка накопите- ля 8 настраивается путем изменения ее содержимого на код, сила которого опре, 50 деляется максимальной кратностью имею-! ших место в ячейках -й страницы накопителя 6 отказов (под силой Ю корректируюшего кода подразумевается его способность

55 обнаруживать ошибки кратности от 1 до Л включительно). Настройка Р -й ячейки накопителя 8 происходит следуюшйм образом.

Информационный выход 9 накопителя 8 соединен с одним входом регпстра 10 силы .корректирующего кода, один из выходов которого связан с информационным входом накопителя 8.

Кодовый выход 11 накопителя 6 соединен с входом регистра 12 кодового слова.

Прямой выход 13 регистра 12 подключен к информационному входу первого блока схем "И 14, инверсный выход 15 регистр ра 12 — к информационному входу второго блока схем "И" 16, выходы блоков 14 и

16 подсоединены к входам первого блока схем ИЛИ 17, выход которого подключен к блоку декодирования 18.

Выход 19 блока 18 связан с блоком управления 20, имеющим вход 21 и выход

22, и с одним из входов триггера 23, Выходы триггера 23 соединены с управляющими входами блоков 14 и 16 соотВ начале работы -страницы накопителя 6, когда отказы в ячейках этой страницы отсутствуют,,) -я ячейка накопителя 8 настраивается на код, исправляюшая способность которого равна, например, .. По

Ф мере накопления в ячейках -й страницы накопителя 6 возникающих в разные моменты времени отказов кратности, например.. (g(k.) кратность имеюших место в некоторых из этих ячеек отказов может достигнуть величины л . При этом сила используемого -й страницей накопителя 6 корректирующего кода с помошью .-йячейки накопителя 8 устанавливается равной (при той же исправляющей способности, равной g). В случае обнаружения в какой-нибудь ячейке .-й страницы накопи теля 6 отказа кратности gag что возможно, когда в ячейке, содержашей )(. 20 кратный отказ, роизойдет отказ кратн сти g, -я ячейка накорителя 8 перестраивается на код с силой ФЬЯ, затем при обнаружении отказа кратности )С+2Я— на код с силой g Ф Я и так далее до

gpss g . Исправляюшая способность корректируюшего кода все время остается постоянной и равной - .

В исходном состоянии триггер 23 сит налом с блока 20 устанавливается в состояние "0 . Для обращения к ячейке J-й страницы накопителя 6 адрес этой ячейки необходимо записать по входу 2 в регистр

1. При этом по адресу, записанному в ре гистр -4, из,,)- -й ячейки накопителя 8 бу дет считано слово, которое определяет си . лу используемого 1 -й страницей накопителя 6 корректируюшего кода. Считанное иэ накопителя 8 слово поступает в регистр

10, после чего блоки 18 и 27 настраиваются на используемый код.

При записи информационное слово по шине 30 поступает в блок 27, с выхода которого кодовое слово через блок схем

"ИЛИ 31 записывается в накопитель 6.

При считывании кодовое слово иэ на копителя 6 поступает в регистр 12, а с прямого выхода 13 регистра 12 через блок схем "И" 14 и блок схем "ИДИ" 17 в блок 18 (считывание кодового слова из накопителя 6 и запись его в регистр 12 могут быть совмещены во времени со считыванием слова из накопителя 8 и записью его в регистр 10). Блок 18 декодирует кодовое слово, определяет наличие или отсутствие неисправимой ошибки в нем, выдавая в соответствии с этим по выходу 19 сигнал в блок 20 и управляя

452037 триггером 23, а также определяет крач» ность имеющей место ошибки (исправимой или неисправимой), информация о чем по- ступает по выходу 22 в схему 25 (в ка-I честве схемы 25 может быть использо-, 5 ван, например, накапливающий сумматор).

В случае отсутствия неисправимой ошибки триггер 23 остается в состоянии

"0". Информационное слово с выхода бло«

18 через блок схем "И" 28 поступает на шину 29.

В случае наличия неисправимой ошибки триггер 23 сигналом с выхода 19 блока

18 устанавливается в состояние "1», подключая инверсный выход 15 регистра 12.

При этом информационное слово на шину

29 не поступает, а обратный код содержащегося в регистре 12 кодового слова с инверсного выхода 15 через блок схем

«И» 32, блок схем "ИЛИ 31 записывает

20 ся в ту же ячейку накопьтеля 6. Палее записанное в накопителе 6 кодовое слово считывается и записывается в регистр 12.

Обратный код нового содержимого регист . ра 12 поступает с инверсного выхода 15

25 через блок схем "И 16, блок схем "ИЛИ

17 в блок 18. Блок 18 декодирует кодовое слово, выдавая через блок схем "И

28 на шину 29 правильное информационЗ0 ное слово, и определяет кратность возможно имеющей место (исправимой) ошибки, информация о которой поступает по выходу 24 в схему 25 и суммируется с прежним содержимым этой схемы.

По окончании считывания (как при наличии, так и при отсутствии неисправимой ошибки) содержимое схемы 25, представляющее собой величину кратности имеюшеro место в ячейке -й страницы накопите40 ля 6 отказа, срав вается схемой 26 с содержимым регистра 10.

Если схема 26 определит равенство кратности имеющего место отказа и силы используемого кода, вся информация из

45 -й страницы накопителя 6 выводится, схема 26 обеспечивает перестройку регистра 10 и блоков 18 и 27 на код, сила которого íà g единиц выше силы предыдущего кода; далее осуществляется ввод информации в -ю страницу накопители 6 и запись в g-ю ячейку накопителя 8 нового слова из регистра 10.

Если кратность отказа не равна (мент ше) силе используемого -й стренипей некопителя 6 корректирующего кода, указанные онерепии (вывел информении из -й страницы. накопителя 6, перестройка регистра 10 и блоков 18 и 27 и т. д.) не производятся и g-я страница накопителя 6. продблжает использовать прежний код.

Предмет изобретения

Запоминающее устройство с автономным контролем, содержащее регистр адреса, подключенный к накопителям, подсоединенным к регистру силы корректирующего кода и регистру кодового слова, блоки кодирования и декодировании, подключенные к регистру силы корректирующего кода и к одному входу схемы сравнения, другой вход которой подсоединен к выходу схемы определения кратности отказа, блоки схем

ИЛИ", выходы которых подключены квходам одного из накопителей и блока декодирования, и блок управления, о т л ич а ю ш е е с я тем, что, с целью упрощения устройства и повышения надежности его работы, оно содержит блоки схем И и триггер, входы которого подключены к выходам блока декодирования и блока управления, а выходы — к управляющим входам первого и второго блоков схем И, информационные входы которых соединены с прямым и инверсным выходами регистра кодового слова, а выходы — с входами первого блока схем ИЛИ, информационные входы третьего и четвертого блоков схем

"И" подключены к одному выходу блока декодирования и к инверсному выходу регистра кодового слова, выходы — к выходной шине устройства и к одному из входов второго блока схем ИЛИ", вход схемы определения кратности отказа подсоединен к другому выходу блока декодирования.

452037

am 20

В.РудФава

Составитель

Texpe> E.ÏîäóðóøèHàK0рректоры. Л.Денисова

Реда rop И.Орлова

Заказ МЬ

Ц14ИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, 113035, Раушская наб., 4

Предприятие «Патент», Москва, Г-59, Бережковская наб., 24 и,. и /gg

Тираж 59 1 Подписное