Узел для сортировки информации

Иллюстрации

Показать всеРеферат

1 (ii) 454548

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 26.05.72 (21) 1789904/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 25.12.74. Бюллетень № 47

Дата опубликования описания 05.02.75 (51) М. Кл. G 06f 7/08

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53I) УДК 681.325.5 (088.8) (72) Автор изобретения

А. Я. Спасибухов

Украинский научно-исследовательский институт мясной и молочной промышленности (71) Заявитель (54) УЗЕЛ ДЛЯ СОРТИРОВКИ ИНФОРМАЦИИ

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ, предназначенных, например, для обработки данных в автоматизированных системах управления.

Известен узел для сортировки информации, содержащий логические элементы «И» и схемы «ИЛИ», схему формирования сквозного переноса, управляющие и информационные шины. В известной схеме узла сортировки информации наличие не участвующих в операции разрядов приводит к холостым тактам, связанным с оперированием этими разрядами, что увеличивает время выполнения всей операции.

Цель изобретения — повышение быстродействия узла адресной подстановки путем исключения холостых тактов.

Для осуществления этой цели узел сортировки информации содержит и-разрядную схему избирательной выдачи, каждый разряд которой состоит из четырех логических элементов «И», причем потенциальные входы первого и второго элементов соединены с соответствующими данному разряду шинами «О» и «1»

«Признак замещения», а потенциальные входы третьего и четвертого элементов «И» соединены с соответствующими данному разряду шинами «О» и «1» «Замещение», импульсные входы первого и второго элементов «И» объединены и соединены с выходом первого элемента «И» предшествующего младшего разряда, причем в младшем разряде импульсные входы первого и второго элементов «И» соединены с управляющей шиной «Такт», выход второго элемента «И» соединен с соответствующей данному разряду шиной «Запись «О» признака замещения» и импульсными входами третьего и четвертого элементов «И», вы10 ходы третьих элементов «И» всех разрядов соединены с соответствующими входами первой схемы «ИЛИ», выход которой соединен с первым входом схемы формирования сквозного переноса; выходы четвертых элементов «И»

15 всех разрядов соединены с соответствующими входами второй схемы «ИЛИ», выход которой соединен с вторым входом схемы формирования сквозного переноса.

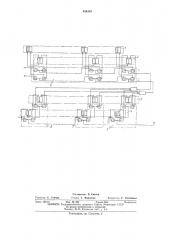

На чертеже дана логическая схема узла

20 сортировки информации.

На схеме приняты следующие обозначения:

1, 2, 3, 4 — n-разрядные регистры чисел АУ (соответствуют числам А, В, С, D), содер кащие схемы «ИЛИ»; 5 — один разряд и-разряд25 ной схемы избирательной выдачи, содержащей элементы «И»; 6 — схема формирования сквозного переноса и 7 — шина «Такт».

Узел сортировки информации осуществляет замену значений разрядов слова А, соответст30 вующих единицам в слове В, значениями взя454548 тых в том же относительном порядке, что и разряды слова А, разрядов слова С, отмеченных единицами в слове D.

Узел для сортировки информации выполняет четырехместную алгебраическую операцию над аргументами А, В, С, и D для хранения которых в арифметическом устройстве, куда входит этот узел, предусмотрены соответственно 1, 2, 3 и 4 регистры. На принципиальной схеме регистры построены из статических триггеров, устанавливаемых в нулевое состояние по левому входу и в единичное по правому. Соответственно, левые выходы триггеров являются нулевыми, а правые единичными.

Узел для сортировки информации построен из схемы избирательной выдачи содержимого регистра 3, состоящего из разрядов 5, соответствующих разрядам регистра 3, каждый из которых содержит по четыре импульсно-потенциальных логических элемента И (на чертеже импульсные входы обозначены стрелками, а потенциальные — точками) и схемы б, формирующей сквозной перенос для передачи значений разрядов слова С к триггерам требуемых разрядов регистров 1 и 2.

Работа узла происходит следующим образом. Перед началом поступления тактовых импульсов значения аргументов должны находиться в своих регистрах. Каждый тактовый импульс проходит сразу до очередного, ближайшего (например, со стороны младших разрядов) участвующего в операции разряда, отмеченного единичным состоянием триггера регистра 4, и опрашивает состояние триггера данного разряда регистра 3, а также устанавливает в нулевое состояние триггер этого же разряда регистра 4 и дальше не проходит.

Установка в нуль указанного триггера обеспечивает сквозной путь до очередного участвующего в операции разряда следующему тактовому импульсу. Сигнал, вырабатываемый в результате опроса состояния триггера регистра 3, по одной из двух цепей, включающих

40 в себя логические схемы ИЛИ, поступает па соответствующий вход схемы б, которая сразу передает его к триггерам требуемых разрядов регистров 1 и 2, и там осуществляется замена значений путем установки триггера регистра

1 в нужное состояние.

Предмет изобретения

Узел для сортировки информации, содержащий логические схемы «ИЛИ», схему формирования сквозного переноса, управляющие и информационные шины, отл и ч а ю щи и с я тем, что, с целью повышения его быстродействия, он содержит и-разрядную схему избирательной выдачи, каждый разряд которой состоит из четырех логических элементов «И», причем потенциальные входы первого и второто элементов соединены с соответствующими данному разряду шинами «0» и «1» «Признак замещения», а потенциальные входы третьего и четвертого элементов «И» соединены с соответствующими данному разряду шинами «0» и «1» «Замещение»; импульсные входы первого и второго элементов «И» объединены и соединены с выходом первого элемента «И» предшествующего младшего разряда, причем в младшем разряде импульсные входы первого и второго элементов «И» соединены с управляющей шиной «Такт», выход второго эле,мента «И» соединен с соответствующей данному разряду шиной «Запись «0» признака замещения» и импульсными входами третьего и четвертого элементов «И»; выходы третьих элементов «И» всех разрядов соединены с соответствующими входами первой схемы

«ИЛИ», выход которой соединен с первым входом схемы формирования сквозного переноса; выходы четвертых элементов «И» всех разрядов соединены с соответствующими входами второй схемы «ИЛИ», выход которой соединен со вторым входом схемы формирования сквозного переноса.

454548

4=

Составитель Э. Сечина

Редактор Е. Гончар

Техред Т. Миронова

Корректор Е. Рогайлина

Заказ 155/10 Изд. № 220 Тираж 624 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4 5

Типография, пр. Сапунова, 2