Устройство для вычисления тригонометрических функций

Иллюстрации

Показать всеРеферат

О П И-"- -АЙЗОБРЕТЕН И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ п> 454564

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 06.02.73 (21) 1883492/18-24 (51) М. Кл, G 06g 7, 22 с присоединением заявки ¹ 1883482/18-24

В УдаРственный комитет (32) Прпори е

Совета Министров СССР ло делам нэобретений и открытий

Опубликовано 25.12.74. Бюллетень № 47

Дата опубликования описания 20.02.75 (53) УДК 681.335(088.8) (72) Авторы изобретения

Л. Д. Будрин и Д. П. Панов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЬ|ЧИСЛЕНИЯ ТРИГОНОМЕТРИЧЕСКИХ

ФУНКЦИЙ

Изобретение относится к области вычислительной техники.

Известны устройства для вычисления функций m tg и т ctg«p, содержащие последовательно соединенные первый элемент сравнения, инвертор, первый интегрирующий усилитель, выход которого подключен ко входу первого модулятора, выход модулятора соединен с первым входом сумматора, а также последочательно соединенные второй элемент сравнения, второй интегрирующий усилитель, выход

«оторого соединен со входом второго элемента равнения и вторым модулятором, выход модулятора соединен со вторым входом сумматора, выход сумматора соединен со входом фазового детектора, выход которого подключен к первому элементу сравнения, а выходы первого и второго элементов сравнения подключены ко вторым входам соответственно второго и первого интегрирующих усилителей.

Известные устройства не позволяют вычислять функции и sec«p и т cosec«p.

Предлагаемое устройство отличается от известных тем, что содержит амплитудный детектор, вход которого соединен с выходом сумматора, а выход подключен к выходу устройства.

Это позволяет расширить класс решаемых задач и повысить точность. 30

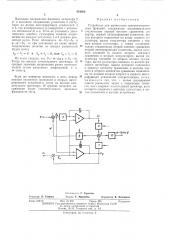

На чертеже изображена схема предлагаемого устройства.

Устройство содержит элементы сравнения 1 и 2, инвертор 3, интегрирующие усилители 4 и 5, модуляторы 6 и 7, сумматор 8, фазовый детектор 9, амплитудный детектор 10.

Устройство работает следующим образом.

К выходам интегрирующих усилителей 4 и 5 подключены соответственно модуляторы 6 и 7, осуществляющие амплитудную модуляцию Bblходных сигналов усилителей двумя синусоидальными напряжениями, сдвинутыми по фазе на 90 . Опорное напряжение модулятора 7 опережает опорное напряжение модулятора 6.

Суммарное выходное напряжение модуляторов

6 и 7 поступает на входы двух детекторов— фазового 9 и амплитудного 10. Фазовый детектор 9 должен работать в линейном режиме, т. е. его выходное напряжение пропорционально сдвигу фаз между входным напряжением и опорным и не зависит от амплитуды входного сигнала. Опорное напряжение фазового детектора 9 совпадает по фазе с опорным напряжением модулятора 6. В этом случае на выходе фазового детектора 9 имеем р = arctg

У, где U, и U — выходные напряжения усилптлей 4 и 5 соответственно.

454564

Предмет изооретепия

pr- cosec g

Составн гель Г. Терехова

Техред Т. Миронова Корректор В. Кочкарева

Редактор О. Степина

Заказ 240/10 Изд. ¹ 233 Тираж 624 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, УК-35, Раушская наб., д. 4)5

Типография, пр. Сапунова, 2

Выходное напряжение фазового детектора 9

cp и выходное напряжение усилителя 5 поступают на входы интегрирующих усилителей 4 и 5, где алгебраически суммируются с входными сигналами m и гр. Если не учитывать динамических ошибок, суммарное входное напряжение на каждом усилителе 4 и 5 должно равняться нулю. Если обозначить m — U.=бгг и гр — cp =6,, то при указанных на схеме знаках подключения величин ко входам усилителей будем иметь — „.:0 и осг+о:О, или i o, О.

Из этого следует, что Ui=-т ctg q; и U=m.

Тогда на выходе амплитудного детектора 10 среднее значение напряжения равно геометрической сумме указанных напряжений, т. е.

m cosec rp.

Если же инвертор включить в цепь между первым элементом сравнения и вторым интегрирующим усилителем, тогда на выходе амплитудного детектора 10 среднее значение напряжения будет соответствовать значению функции m sec cp. 25

Устройство для вычисления тригонометрических функций, содержащее последовательно соединенные первый элемент сравнения, инвертор, первый интегрирующий усилитель, выход которого подключен ко входу первого модулятора, выход модулятора соединен с первым входом сумматора, а также последовательно соединенные второй элемент сравнения. второй интегрирующий усилитель, выход которого соединен со входом второго элемента сравнения и вторым модулятором, выход модулятора соединен со вторым входом сумматора, выход сумматора соединен со входом фазового детектора, выход которого подключен к первому элементу сравнения, а выходы первого и второго элементов сравнения подключены ко вторым входам второго и первого интегрирующих усилителей соответственно, о т л ич а ю щ е е с я тем, что, с целью расширения класса решаемых задач и повышения точности, оно содержит амплитудный детектор, в од которого соединен с выходом сумматора, а выход подключен к выходу устройства.