Троичный сумматор

Иллюстрации

Показать всеРеферат

O П И С A Н И E 455339

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (G1) Зависимое от авт. свидстельства— (22) Заявлено 06.06.72 (21) 1792818/18-24 с присоединением заявки №вЂ”, 32) Приорнrст —Опубликоваио 30.12.74. Бюллетень М 48

Дата опубликования описания 01.03.75 (5!) Ч.lхл. G OGf 7/385 государственный комитет

Совета Министров СССР по делам изобретений и OTKpblTMM (53) УД1х 681.3 5.54 (088.8) (72) Авторы изобретения

Б. А. Солдатов, Н. T. Пластун и В. Ф. Павлов (71) Заявитель (54) ТРОИЧНЫЙ СУММАТОР

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах с троичной системой счисления.

Известны троичные сумматоры двух слагаемых, состоящие из двух полусумматоров, включенных последовательно, когда на вход первого полусумматора подаются слагаемые, а на вход второго — частичная сумма и окончательный перенос, собранный по схеме «ИЛИ» из переносов первого н второго полусумматоров и задержанньш на один такт.

Предложенный троичный сумматор двух слагаемых, имеющий два последовательна включенных двухступенчатых полусумматора, отличается тем, что в его второн полусум»атор введен дополнительный логический троичный элемент, первый и второй входы которого связаны соответственно с первы» и четвертым выходами первой ступени второго полусумматора, второй и третий входы объединены и через линшо задержки соединены с выходом !астичной суммы псрвого полусумматора, а выход — с дополнительным входом первой ступени второго иолусумматора. Выходы частичной суммы и промежуточного переноса соединены по схеме «ИЛИ» it подключены к входу первой ступени второго полусумматора.

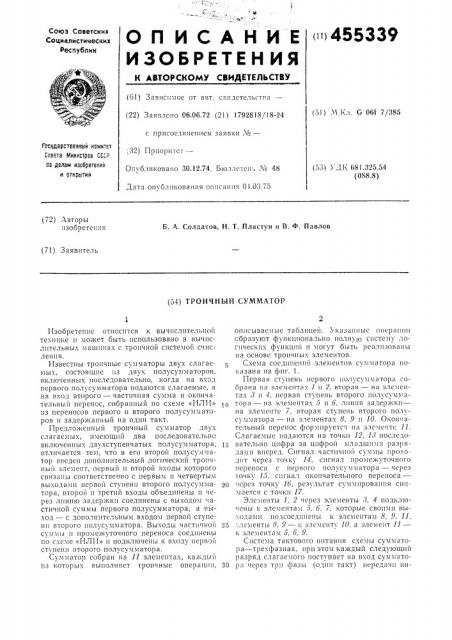

Сумматор собран иа 11 элементах, каждьш из которых выполняет троичные операции, описываемыс таблицей." .казаииыс операции образуют функционально полную систему логических функций и могут быть реализованы на основе троичиых элементов.

Схема соединений элементов сумматора показана иа фиг. 1.

Первая ступень первого полусумматора собрана иа элементах 1 и 2, вторая — на элементах 8 и 1, первая ступень второго полусумматора — на элементах 5 и 6, линия задержки— на элементе 7, вторая ступень второго полусумматора — иа элемента < 8. 9 и 10. Окон .ательный перенос формируетс: иа элементе 11.

Слагаемые подаются на точки 12, 18 послсдо1; Bàòåëüíо цифра за цифрой младшими разпядами вперед. Сигнал частичной суммы проходит через точку 14, сигнал промежуточного переноса с первого полусумматора — через точку 15, сигнал окончательного переноса—

2р срез точку 16, результат суммирования снимается с точки 17.

Элементы 1, 2 через элементы 8, 4 подключены к элементам 5. 6, 7, которые своими выходами подсоединены к элементам 8, 9, 11, 25:-:лементы 8, 9 — к элементу 10, а элемент 11— к элементам 5, 6, 9.

Система тактового llIITBH11H схемы сумматора — трехфазиая. при этом каждый следующий разряд слагаемого поступает иа вход сумматоЗр ра через три фазы (одии такт) передачи ин455339

Вхол

3 ) 4!

Выход!

О

О

О

О

1

О

l ! !

+.

О

+- !

+.1

w+- !

+-!

О

+l

+.1

l

О

О

+.

О

- -

О

+1

+1

О

+1

-!- 1

1-1 -1

О

О

w!

О

О !

- 1

-l

О

+1

+! — —

+1

Π— 1

О

О

О

+!

+! — 1 —

+- формации по элементам схемы (фиг. 2).

Рассмотрим работу сумматора на примере суммирования двух положительных чисел 2 и

12. Первое слагаемое — число 2 в троичной системе счисления с симметричным расположением цифр (+1,0 — 1), где знак числа оиоеделяется знаком старшего разряда, прсдставляется отрицательным сигналом в первом разряде и положительным во втором. Второе слагаемое — число 12 представляется отсутствием сигнала в первом разряде и положительными сигналами во втором и третьем разрядах.

Отрицательный сигнал первого разряда первого слагаемого подается на входы вх.! элемента 2 и вх.э элемента 4 (фиг. 1, 2).

Тактовым импульсом первой фазы первого такта считывается информация с элемента 2 и согласно логике работы элемента, записанной в таблице, положительный сигнал с элемента 2 передается на входы вх.3 элемента 8 и вх.! элемента 4. Импульсом второй фазы отрицательный сигнал частичной суммы с элемента 8 подается на входы вх.4 элемента б и вх.4 элемента 7. Импульсом третьей фазы отрицательный сигнал с элемента б поступает иа входы вх.4 элемента 8 и вх.) элемента 11, а с элемента 7 — на вход вх.3 элемента 11. Одновременно положительный сигнал второго разряда первого слагаемого подается на входы вх.; элемента 1 и вх.q элемента 4, а второго слагаемого — на вх. элемента 1.

Импульсом первой фазы второго такта отрицательный сигнал с элемента 8 передастся суммы, а положительный сигнал окончательного переноса второго полусумматора с элемента 11 подается на входы вх.! элемента 5 и вх.2 элемента 9. Положительный сигнал с элемента 5 импульсом третьей фазы передается на входы вх.! элемента 8 и вх.4 элемента 9.

Импульсом первой фазы пятого такта положительньш сигнал с элемента 8 передается на вход вх.! элемента 10, импульсом второй фазы положительный сигнал с элемента 10 выходит из сумматора, образуя четвертый разряд суммы.

Таким образом, цифры соответствующих иа вход вх.4 элемента 10, импульсом второй фазы отрицательньш сигнал с элемента 10 выходит из сумматора, образуя первый разряд суммы, а положительный сигнал промежуточ-!!ого переноса первого полусумматора с поразрядным весом 2" (n — номер разряда) с элемента 4 подается на вход вх.з элемента б.

Импульсом третьей фазы отрицательный сигнал с элемента б поступает на входы вх. элемента 8 и вх.i элемента 11. Одновременно положительный сигнал третьего разряда второго слагаемого проходит иа вход вх.4 элемента 1.

Импульсом первой фазы третьего такта от15 рицательиый сигнал с элемента 1 передается иа вход вх.2 элемента 8, отрицательный сигнал с элемента 8 — иа вход вх.4 элемента 10. Положительный сигнал частичной суммы с элемента 8 импульсом второй фазы поступает иа

20 вход вх.3 элемента 5 и вход вхи элемента 7, а положительный сигнал окончательного переноса второго иолусумматора с поразрядным весом 3" (и — номер разряда) с элемента 11 на входы вх.> элемента 5 и вх.2 элемента 8; отри25 цательньш сигнал выходит с элемента 10, образуя второй разряд суммы. Положительньш сигнал с элемента 7 импульсом третьей фазы передается на вход вх. элемента 11.

Импульсом первой фазы четвертого такта 0 положительный сигнал с элемента 9 поступает на вход вх.э элемента 10, импульсом второй фазы отрицательный сигнал с элемента 10 выходит из сумматора, образуя третий разряд

Условное обозначение элемент;1 разрядов суммы появляются на выходе су.мматора спустя 1 такт и 2 фазы с момента по55 дачи их на вход сумматора.

Предложенныи сумматор позволяет также получить алгебраическую сумму отрицатепьиых и разнознаковых чисел.

60 Предмет изобретения

Троичный сумматор, содержащий два последовательно соединенных двухступенчатых полусумматора, отличающсшся тем, что, с целью

65 увеличеш!я быстродействия, второй полусум455339

17 матор содержит дополнительный логический троичный элемент, первый и второй входы ко-торого соединены соответственно с первым и четвертым выходами первой ступени второго полусумматора, второй и третий входы объединены и через линьио задержки соединены с выходом суммы первого полусумматора, а выход соединен с дополнительным входом второго полусумматора.

455339

9ааза, Ц И(1П ЛЬСЫ ФДРХфД ЯОХД ч цстоуиина питаииЯ вЂ” — 4аг7 бсб „ 7 — 3cnuca „

Составитель Н. Милославская

Тскрсд Г. Васильева

Корректор Е Кашина

Редактор И. Грузова

Изд. Л 19б7 тираж 624

Ш1ИИПИ Государственного комитета Совета Министров CCCP по делам изобретений и открытий

Москва, )К-35, Раушская наб., д. 4/5

Подписное

3".t ÿ-. 120

Обл. тип. Костромского управления издательств, полиграфии и книжной торговли

Яиа 7аазау

79

17

76

+ ь уитыбание „+1 " Считыбани „7 " т а 2