Устройство для исправления ошибок при параллельном считывании двоичной информации

Иллюстрации

Показать всеРеферат

(!и455352

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства 292175 (22) Заявлено 18.07.72 (21) 1812468/18-24 (51) М.Кл. 6 06k 5,704 с присоединением заявки №вЂ”

)1 осударственный комитет

Совета Министров СССР оо делам изобретений и открытии (32) Приоритет—

Опубликовано 30.12.74. Бюллетень ¹ 48

Дата опубликованы!я описания 04.05.75 (53) УДК 681.327.11 (088.8) .(72) Авторы изобретения

В. И. Дмитриев и А. В. Иванов (71) Заяв1пель

Московский ордена Ленина энергетический институт (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК

ПРИ ПАРАЛЛЕЛЬНОМ СЧИТЫВАНИИ ДВОИЧНОЙ

ИНФОРМАЦИИ

Устройство для исправления ошибок ири иараллслы1ом считывании двоичной информации относится к области вычислительной техники и может быть использовано в устройствах записи — воспроизведения двоичной информ»ции.

Известное устройство для исправления оигибок Ilptl параллельном считывании двоичной информации по авт. св. 292175 позволяет исправлять искаженные символы, расположен>иые на нескольких дорожках носителя, путем добавления «otnpoat»tt,tv символов ио строке и д1гагонали.

Однако при некоторых вариантах располо>неHIIH искажсttttbtx симВолоВ olio может Осу - 15

lцествлять ложные «испраВления» !!еискажеи.ИЫХ СИМВОЛОВ.

Цель изобретения — повышение эффективности коррекпнн ошибок.

Это достигается тем, что в устройство введены схемы «НЕ», входы которых подключены к выходам ячеек памяти, а выходы — к соответствующим входам схем «И».

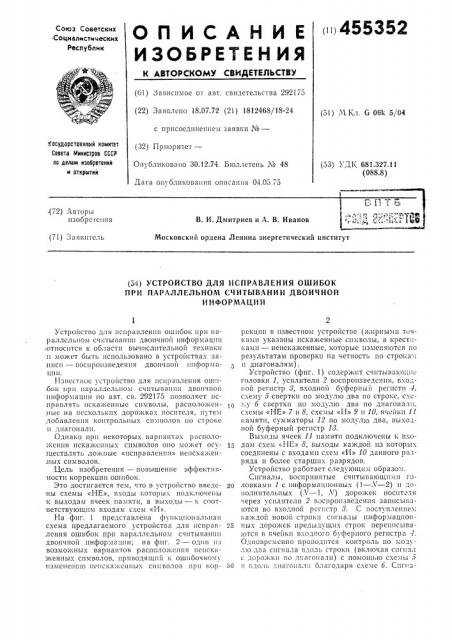

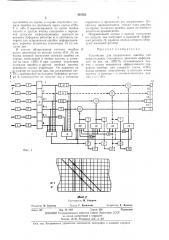

На фнг. 1 представлена (1)уикциональиая схема предлагаемого устройства для неправ- 25 .лення ошибок при параллельном считывании двоичной информа IIIH; на фиг. 2 — один 113

ВОзмО>кных вариантов расположения исиcl«l

>кенных снмво IQB, приводящий к ошибочно»у изменению поиска>кениых символов Ilt)II кор- ВО рскции в известном устройстве (жирными точк ай!и указаны искаженные символы а крест. I ками — неискаженные, которые изв!е!1я!отея по результатам проверки па четность по строка.. и диагоналям).

Устройство (фиг. 1) содержит считывающи .. голонки I, усилители 2 воспроизведения, вход1:oi регистр 8, входной буферный регистр 4, схему 5 свертки по модулю два по строке, схему б свертки по модулю два IIO диагонали. схемы «НЕ» 7 и 8, схемы «И» 9 и 10, ячейки 11 памяти, сумматоры 12 по модул!о два, выходной буферный регистр 18.

Выход!,! ячеек 11 памяти подключены к входам схем «НЕ» 8, гыходы каждой из которых соединены с входами схем «И» 10 данного разряда и более старших разрядов.

Устройство работает следующим образом.

Сигналы, воспринятые считывающими головками 1 с информационных (1 — Л вЂ” 2) и дополнительных (Л вЂ” 1, Л ) дорожек носителя через усилители 2 воспроизведения записыгаются во входной регистр 8. С поступлением каждой новой строки сигналы ш1формациониых дорожек предыдущих строк переписыва-!

Отся в ячейки входного буферного регистра 4.

Одновременно проводится контроль по мог,лю два сигнала вдоль строки (включая сигнал с дорожки по диагонали) с помощью схе;III б

„вдоль:!иагоиал.t благодаря схеме б. Сип!а455352

Пред.låт изобретеllия

Фиг. г

Составитель М. Сидоров

Текред Г. Васильева

lхорректор Е. Кашина

Редактор И. Грузова

Заказ 120 Изд. № 1967 Тираж 624 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, К-35, Раушская наб., д. 4/5

Сбл. тип. Костромского управления издательств, полиграфии и книжной торговли лы ошибки по строке B случае отсуTcTB115I сигнала ошибки по диагонали через схемы «НЕ»

7 и «И» 9 переписываются из одной ячейки памяти в другую ячейку синхронно с переда«ei сип1алов информационных дорожек во входном буферном регистре 4, в диагональ которого для исправления ошибок информационных дорожек включены сумматоры 12 по модулю два.

Б случае обнаружения сигнала о1иибки вдоль диагонали иа выходе схемы «И» 10, на входы которой поступают сигналы ошибки по строке, записанный в ячейке памяти, и сигналы со схем «НЕ» 8 при условии отсутствия сигналов ошибки в других ячейках памяти, возникает сигнал коррекции. Ои подается иа су мматор по модулю два, где искаженный сига иал, храиягцийся BO входном буферном регистре 4, суммируется по модулю 1ва с сигналом

К01>рекции li происходит его исправление. Носкольку предполагается только oдиа Ошиока по строке, то сигнал 011III61(II далее пo ячейкам памяти ие продвигается.

Исправленный сигнал с выхода сумматора ио модулю два поступает в выходной буфср11ый регистр 18, крайние ячейки которого образуют выходной регистр.

Устройство для исправления ошибок ири параллельном считыван1ш двоичной информации пo авт. св. 292175, отличающееся тем, 15 что, с целью повышения эффективности коррскцllll ошибок, оно содерж11з схемы «НЕ», входы которых подключены к выходам ячеек паi 1яти, а выходы — I(соотвстству tolIIIIAI дам cxci «И».