Устройство для контроля оперативного накопителя информации

Иллюстрации

Показать всеРеферат

О 11 И С А Н И Е 455375

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. сгндетельства— (22) Заявлено 04.09.72 (21) 1824528/18-24 (51) М. Кл. G 11с 29:00 с присоединением заявки—

Государственный комитет

Совета Министров СССР по делам изобретений н открытий (32) Приоритет—

Опубликовано 30.12.74. Бюллетень М 48

Дата опубликования описания 0.03.75 (53) УДК 681.327.17 (088.8) (72) Авторы изобретения

Л. К. Самойлов и В. В. Битков (71) Заявитель

Таганрогский радиотехнический институт (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОПЕРАТИВНОГО

НАКОПИТЕЛЯ ИНФОРМАЦИИ

Изобретение относится к запоминающим устройствам.

Известно устройство для контроля оперативного накопителя информации, содержащее блок формирователей, блок усилителей, входы которого подсоединены к входным шинам устройства, а выходы, начиная со второго,.— к входам одной группы схемы сравнения, блок управления.

Устройство реализует тесты типа «дождь», «шахматный порядок», «бегающая единица» и др.

Однако в таком устройстве затруднены визуальный контроль прохождения теста и аппаратурная реализация. Кроме того, оно не обеспечивает равномерного характера распределения единиц и нулей.

Предлагаемое устройство отличается от известного тем, что оно содержит схемы задержки и одноразрядный сумматор, причем один из входов сумматора подключен к первому выходу блока усилителей и входу одной из схем задержки, выходы которой подсоединены к входам другой группы схемы сравнения, другой вход сумматора — к блоку управления, а выход — к первому входу блока формирователей и входу другой схемы задержки, выходы которой соединены с остальными входами блока формирователей.

Это позволяет упростить устройство и повысить точность контроля.

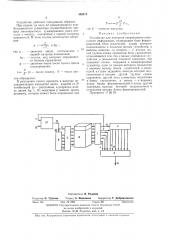

На чертеже показана блок-схема предлагаемого устройства.

Устройство содержит блок 1 усилителей, входы которого подсоединены к входным шинам 2 устройства, а выходы 3, начиная со второго, — к входам 4 одной группы схемы 6 сравнения, блок управления (на чертеже ие то показан), блок 6 формирователей, выходы которого подключены к выходным шинам 7 устройства, схемы 8 и 9 задержки и одноразрядный сумматор 10. Вход 11 сумматора подключен к первому выходу 8 блока усилителей и

15 входу,12 схемы 9 задержки, выходы которой подсоединены к входам 18 другой группы схемы б сравнения. Вход 14 сумматора и выход 16 схемы сравнения соединены с блоком управления. Выход 16 сумматора подключен к перво2О му входу 17 блока 6 формирователей и входу 18 схемы 8 задержки, выходы этой схемы задержки — к входам 17 блока 6, начиная со второго.

Выходные шины 7 и входные шины 2 устройства подсоединяются к контролируемому оперативному накопителю 19, при этом первые шины 2 и 7 (верхние на чертеже) — к первой матрице накопителя. (В устройстве вместо схем задержки могут быть использованы регистры сдвига.) 455375

T. вов = 2 — ? „вв о р где Z — емкость матрицы.

Составитель В. Рудаков

Редактор И. Грузова Техред А. Васильева Корректор Т. Добровольская

Изд. Ко 1965 Тираж 591 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, ?К-35, Раушская наб., д. 4/5

Заказ 124

Обл. тип, Костромского управления издательств, полиграфии и кни киой торговли>

Устройство работает следующим образом.

Прп подаче «а вход i?4 одноразрядного комбинационного сумматора осуществляется процесс многократного суммирования этого сигнала с числом, считанным с первой матрицы нако«птеля. В этом случае реализуется опе1зация

Л и i + i = Х ??, + 5g (,! —,1

10 где y; — двоичное число, считываемое с первой матрицы накопителя;

Лу; — сигнал, код которого определяется блоком управления; у †: — двоичное число после одного цикла

15 суммирования; 1

n= — (n — целое число), Ж вЂ” число цикZ лов обращения.

В результате такого процесса в матрице последовательно находятся числа каждой из 2" комбинаций (р — расстояние, в разрядах, между двумя Лу ). От величины р зависит время проверки, которое может быть определено как

Предмет изобретения

Уст1зойство для контроля оперативного накопителя информации, содержащее блок формирователей, блок усилителей, входы которого подсоединены к входным шинам устройства, а выходы, начиная со второго, — к входам од«ой группы схемы сравнения, блок управления, отличающееся тем, что, с «елью упрощения устройства и повышения точности контроля, о«о содержит схемы задержки и одноразрядный сумматор, один «з входов которого подключен и первому вь1ходу блока усилителей и входу одной из схем задержки, выходы которой подсоединены к входам другой группы схемы срав«ения, другой вход сумматора подключен к блоку управления, а выход к первому входу блока формирователей и входу

Приоритет 17.06.70.