Устройство цикловой синхронизации

Иллюстрации

Показать всеРеферат

455503

Союз Советских

Социалистических еспубпик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 06.02.73 (21) 1879038/26-9 с присоединением заявки ¹â€” (32) Приоритет—

Опубликовано 30.12.74. Бюллетень ¹ 48

Дата опубликования описания 05.09.75 (51) М. Кл. Н 041 7/04 государственный комитет

Совета Министров СССР

1а делам изобретений и открытий (53) УДК 621.394.73 (088.8) (72) Авторы изобретения

М. Л. Миневич, А. Л. Шапиро и Ю K. Левашов ь. р (71) Заявитель (54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к области техники связи и может использоваться в системах передачи информации.

Известно устройство цикловой синхронизации, содержащее приемный регистр и блок управления.

Цель изобретения — упрощение устройства и сохранение постоянства схемы прп смене вида синхрогруппы.

Это достигается тем, что в предлагаемое устройство цикловой синхронизации введен формирователь синхрогрупп, охваченный обратной связью, выход которого соединен с одним из входов логического элемента, второй вход которого связан с выходом приемного регистра, также охваченного цепью обратной связи через одну из схем «И», другой вход которой подключен к блоку управления, при этом выход схемы «И» подсоединен к входу схемы «ИЛИ», выходом подключенной к выходу приемного регистра, выход логического элемента подключен к одному из входов другой схемы «И», второй вход которой связан с блоком управления, а выход — с вхо.дом пороговой схемы, гпричем каждая ячейка приемного регистра и формирователя синхрогрупп соединена с блоком управления.

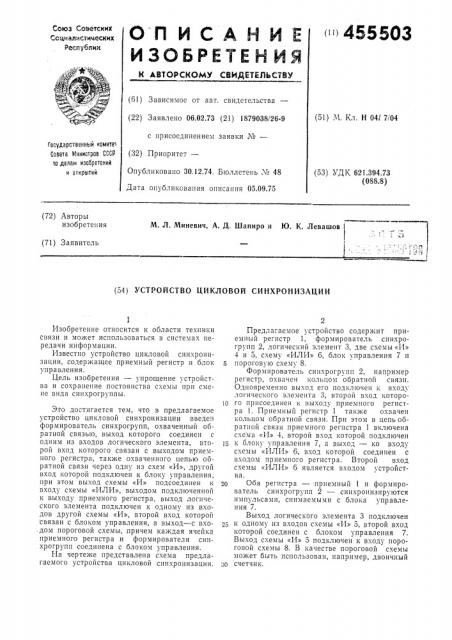

На чертеже представлена схема предлагаемого устройства цикловой синхронизации.

Предлагаемое устройство содержит приемный регистр 1, формирователь синхрогрупп 2, логический элемент 3, две схемы «И»

4 и ", схему «ИЛИ» 6, блок управления 7 и

5 пороговую схему 8.

Формирователь синхрогрупп 2, например регистр, охвачен кольцом обратной связи.

Одновременно выход его подключен к входу логического элемента 3, второй вход которо1О го присоединен к выходу приемного регистра 1. Приемный регистр 1 также охвачен кольцом обратной связи. При этом в цепь обратной связи приемного регистра 1 включена схема «И» 4, второй вход которой подключен к блоку управления 7, а выход — ко входу схемы «1ЛЛИ» 6, вход которой соединен с входом приемного регистра. Второй вход схемы «ИЛИ» 6 является входом vcTpoHcTва.

2р Оба регистра — -приемный 1 и формирователь синхрогрупп 2 — синхронизируются импульсами, снимаемыми с блока управления 7.

Выход логического элемента 3 подключен к одному из входов схемы «И» 5, второй вход которой соединен с блоком управления 7.

Выход схемы «И» 5 подключен к входу пороговой схемы 8. В качестве пороговой схемы может быть использован, например, двоичный зо счетчик.

455503

l0

3О

5О

Для случая, когда синхрогруппа длиной п двоичных символов полностью передается перед командой, устройство работает следующим образом.

Очередной приходящий импульс с входа схемы «ИЛИ» 6 записывается в приемный регистр. После этого начинается процесс обработки информации. Блок управления производит последовательно п сдвигов в приемном регистре и в формирователе синхрогрупп.

С ема «И» 4.работает как управляемый ключ, т. е. при записи приходящего символа ключ разомкнут, а при обработке информации ключ замкнут. Процесс обработки информации происходит со скоростью большей, чем скорость передачи. Это возможно в том случае, когда выполняется условие т(Т, (1) где n — число символов в синхрогруппе; т — время срабатывания дискретных элементов — период следования импульсов сдвига обработки информации;

Т вЂ” период следования приходящих импульсов.

Символы с приемного регистра 1 и формирователя синхрогрупп 2 поступают на вход логического элемента 3 — сумматора по модулю 2, который, как известно, реализует функцию Jt=x(xgVx)xg, т. е. выявляет несовпадения между известными символами синхрогруппы с формирователя синхрогруппы 2 и приходящими символами с приемного регистра 1.

Сигнал с выхода сумматора по модулю 2, проходя через схему «И» 5, работающую как ключ, управляемый устройством управления (ключ замкнут на время обработки информации и разомнут остальное время) попадает на пороговую схему 8, где фиксируется число несовпадений. В случае превышения порога t (t — число исправляемых ошибок в синхрогруппе) с выхода порогового устройства

8 следует сигнал запрета. На этом процесс обработки информации заканчивается. Из-за наличия обратной связи, после п сдвигов символы в обоих регистрах оказываются записанными так же, как до обработки информации.

В этом случае, когда символы цикловой синхронизации смешаны с командными символами по известному заранее закону, приходится увеличивать длину приемного регистра по A =n,+и,, где n, — число знаков в синхрогруппе; п — число знаков в команде).

При этом устройство управления производит сдвиг одновременно в обоих регистрах в том случае, когда в последней ячейке приемного регистра находится символ синхрогруппы. Если же в ней находится командный символ, сдвиг производится только в приемном регистре, а «ключ» «И» 5 на это время размыкается.

Условие (1) при этом преобразуется в

N«T. (2)

С увеличением п количество элементов растет пропорционально п (увеличивается длина приемного регистра, формирователя синхрогрупп и пропорционально log> (n — t) длина двоичного счетчика — порогового устройства), тогда как в известном дешифраторе количество элементов с увеличением п растет приблизительно пропорционально С, .

Предмет изобретения

Устройство цикловой синхронизации, содержащее приемный регистр и блок управления, отлича ощееся тем, что, с целью упрощения устройства и достижения постоянства схемы при смене вида синхрогруппы, в него введен формирователь синхрогрупп, охваченный обратной связью, выход которого соединен с одним из входов логического элемента, второй вход которого связан с выходом приемного регистра, также охваченного цепью обратной связи через одну из схем «И», другой вход которой подключен к блоку управления, при этом выход схемы «И» подсоединен к входу схемы «ИЛИ» выходом подключенной к входу приемного регистра, выход логического элемента подключен к одному из входов другой схемы «И», второй вход которой связан с блоком управления, а выход — с входом пороговой схемы, причем каждая ячейка приемного регистра и формирователя синхрогрупп соединена с блоком управления.

455503

1 Раарешени

Составитель Е. Ковалева

Текред Т. Курнлко

1(оррсктор И. Учакииа

Редактор Е, Караулова

Заказ 2072

МОТ, Загорский филиал

Изд. № 1073 Тираж 678 Подписное

ЦНИИПИ Государственного комитета Совета Министров CCCP по делам нзобретен.ш и открытий й!осква, 71(-35, Раугнская наб., л. 4)5