Устройство для сравнения по фазе двух электрических величин

Иллюстрации

Показать всеРеферат

1 — у.1 ())) 456337

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (51) М. Кл. Н 02h 3 38 (22) Заявлено 21.12.72 (21) 1860897/24-7 с присоединением заявки №

Государственный комитет

Совета Министров СССР (32) Приоритет

Опубликовано 05.01.75. Бюллетень № 1 по делам изобретений (53) УДК 621.316.925 (088.8) и открытий

Дата опубликования описания 08.07.75 (72) Авторы изобретения

В. Л. Карцев и Д. Р. Любарский (71) Заявитель Всесоюзный государственный проектно-изыскательский и научно-исследовательский институт энергетических систем и электрических сетей (54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ПО ФАЗЕ ДВУХ

ЭЛЕКТРИЧЕСКИХ ВЕЛИЧИН

Предлагаемое устройство относится к области релейной защиты и автоматики, а именно к области построения быстродействующих измерительных органов на основе схем сравнения по фазе двух электрических величин.

В настоящее время актуальной задачей является создание сверхбыстродействующих защит для сильнонагруженных линий электропередач переменного тока сверхвысокого напряжения 500 — 1150 кв с целью сохранения устойчивой работы мощных энергосистем при коротких замыканиях.

Известны устройства сравнения по фазе двух электрических величин, содержащие схему сравнения времени совпадения мгновенных значений указанных величин и схему сравнения времени несовпадения этих же величин с заданным временем. Однако измерение времени несовпадения осуществляется косвенно путем формирования вспомогательного импульса через заданное время после окончания сигнала совпадения, Такое выполнение схемы сравнения времени несовпадения приводит к значительному снижению помехоустойчивости устройства, так как схема сравнения времени несовпадения содержит несколько элементов, работающих от импульсных сигналов, которые могут оказаться ложными.

Цель изобретения — повысить быстродействие устройства и обеспечить независимость его от заданного времени, а также повышать его помехоустойчивость.

Указанная цель достигается тем, что входы схемы сравнения времени совпадения и схемы сравнения времени несовпадения объединены, а их выходы присоединены к элементу

«ИЛИ», причем схема сравнения времени не10 совпадения содержит подключенный ко входам устройства формирователь импульсов, соединенный со входом элемента «И», два других входа которых подсоединены ко входам устройства непосредственно и через инвертор, 15 а выход элемента «И» соединен с выходом формирователя импульсов, через первый элемент «Запрет» и элемент задержки на возврат — со входом второго элемента «Запрет», а инверсные выходы первого и второго эле20 ментов «Запрет» соединены с выходом элемента «И», соответственно, через элемент задержки на срабатывание и непосредственно.

При этом условие срабатывания для схемы

25 сравнения времени совпадения следующее:

tc +w зад.c где t, — время совпадения сравниваемых электрических величин l> и 1 ., 30 t.,„, — заданное время совпадения, 456337 где

Условие срабатывания для схемы сравнения времени несовпадения следующее:

t„ (33Д.Н

t„=0,5Т вЂ” 1С вЂ” время несовпадения

lI и Iq, зад.н=0,5T — t3aq c — заДанное вРемЯ несовпадения;

T=20 Мсек — период промышленной частоты.

В предлагаемом устройстве при двухполупериодном его выполнении в течение половины периода промышленной частоты осуществляется сравнение по одному из двух названных условий, либо в схеме совпадения, либо в

СХЕМЕ НЕСОВПаДЕНИЯ, И НЕЗаВИСИМО От t3ag, (т. е. от вида характеристики срабатывания) максимальное время срабатывания не будет превышать 10 мсек.

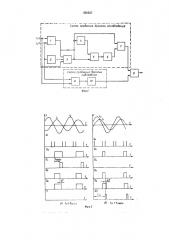

На фиг. 1 приведена принципиально-структурная схема предлагаемого устройства сравнения двух электрических величин 1 и Iq no фазе при однополупериодном выполнении; на фиг. 2 приведены диаграммы, поясняющие работу схемы сравнения времени несовпадения для случаев н) зад.н (a) гДе t (t33g н (б), где 1 — формирователь импульсов, на выходе которого появляются импульсы в момент перехода одной из сравниваемых величин Ii или I через нуль; 2 — инвертор; 3 — элемент

«И»; 4 — элемент задержки на срабатывание;

5 — первый элемент Запрет»; 6 — элемент задержки на возврат; 7 — второй элемент «Запрет»; 8 — элемент «ИЛИ»; 9 — элемент «И»;

10 — элемент задержки на срабатывание.

Работа схемы сравнения времени совпадения величин,l< и I> с заданным временем известна, поэтому пояснения требует работа схемы сравнения времени несовпадения величин

lI и 4 с заданным временем.

Наличие несовпадения 1 и 4, начало которого фиксируется импульсами от формирователя импульсов 1, появляющимися в момент перехода одной из величин I или I> через нуль, определяется элементом 3.

При выполнении условия срабатывания для схемы несовпадения появляется сигнал на выходе элемента 7. Для правильной фиксации времени несовпадения l и Iq сигнал на выхо5

Зо

50 де 7 должен появляться только по окончании несовпадения I и I>. Поэтому при наличии несовпадения величин I и I>, фиксируемого появлением сигнала на выходе элемента 3, на вход 7 подается сигнал запрета от 3, который снимается по окончании несовпадения li и I .

Для того, чтобы схема несовпадения сработала при выполнении условия срабатывания по окончании несовпадения, разрешающий сигнал на входе (7) за счет наличия элемента задержки на возврат (6) держится по окончании несовпадения,l и I> в течение времени At>, достаточного для срабатывания (7) (М составляет доли миллисекунды).

В случае невыполнения условия срабатывания (при (t<)t3ag.н) через время 133д.н, определяемое элементом задержки на срабатывание (4), с выхода последнего поступает сигнал на (5), запрещающий действие схемы сравнения времени несовпадения.

На фиг. 2 приведены UI — сигнал на выходе (1), U3 — сигнал на выходе (3), U4 — сигнал на выходе (4), Us — сигнал на выходе (5), У3 — сигнал на выходе (6), U7 — сигнал на выходе (7).

Предмет изобретения

Устройство для сравнения по фазе двух электрических величин, содержащее схему сравнения времени совпадения мгновенных значений указанных величин и схему сравнения времени несовпадения тех же величин с заданным временем, отличающееся тем, что, с целью повышения быстродействия и обеспечения независимости его от заданного времени, а также для повышения помехоустойчивости, входы схем сравнения объединены, а их выходы присоединены к элементу

«ИЛИ», причем схема сравнения времени несовпадения содержит подключенный ко входам устройства формирователь импульсов, соединенный со входом элемента «И», два других входа которого подсоединены ко входам устройства непосредственно и через инвертор, а выход элемента «И» соединен с выходом формирователя импульсов через первый элемент «Запрет» и элемент задержки на возврат — со входом второго элемента «Запрет», а инверсные входы первого и второго элементов «Запрет» соединены с выходом элемента

«И», соответственно, через элемент задержки на срабатывание и непосредственно.