Фазовый дискриминатор

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (п) 456349

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства— (22) Заявлено 24.10.72 (21) 1839424/26-9 с присоединением заявки № (32) Г1риоритет

Опубликовано 05.01.75. Бюллетень № 1

Дата опубликования описания 11.03.75 (51) М. Кл. Н 03d 13/00

Н 03k 5/20

Государственный комитет

Совета Министров СССР (53) УДК 621.374(088.8) по делам изобретении н открытий (72) Авторы изобретения

P. Д. Бай и Г. Н. Широченко (71) Заявитель (54) ФАЗОВЫИ ДНСКРНМННАТОР

h = ah+ah.

Изобретение относится к радиотехнике, может быть использовано в системах автоматического управления в .качестве устройства сравнения фаз сигналов задания и обратной связи.

Известны фазовые дискриминаторы, содержащие блок преобразования разности фаз в широтный,импульс, фазовый компаратор, источники входных напряжений и интегрирующие конденсаторы.

Цель изобретения — повышение быстродействия — достигается тем, что источники входных напряжений предлагаемого дискриминатора, подключены к блоку преобразования разности фаз в широтный импульс, к фазовому компаратору и к блоку сигналов разряда, соединенному также с фазовым компаратором, а интегрирующие конденсаторы подключены соответственно через генераторы тока к блоку преобразования разности фаз в широтный импульс, через разрядные устройства— к блоку сигнала разряда и к схеме выделения сигнала с большей амплитудой.

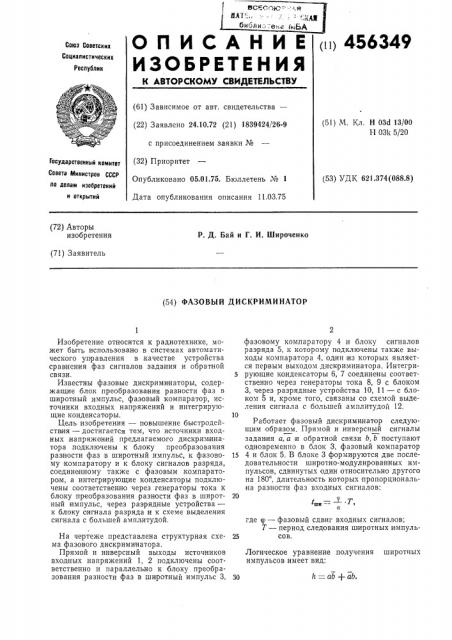

На чертеже представлена структурная схема фазового дискриминатора.

Прямой и инверсный выходы источников входных напряжений 1, 2 подключены соответственно и параллельно к блоку преобразования разности фаз в широтный импульс 3, фазовому комларатору 4 и блоку сигналов разряда 5, к которому подключены также выходы компаратора 4, один яз которых является первым выходом дискриминатора. Интегри5 рующие конденсаторы 6, 7 соединены соответственно через генераторы тока 8, 9 с блоком

3, через разрядные устройства 10, 11 — с блоком 5 и, кроме того, связаны со схемой выделения сигнала с большей амплитудой 12.

Работает фазовый дискриминатор следующим образом. Прямой и инверсный сигналы задания а, а и обратной связи b, b поступают одновременно в блок 3, фазовый компаратор

15 4 и блок 5. В блоке 3 формируются две последовательности широтно-модулированных импульсов, сдвинутых один относительно другого на 180, длительность которых пропорциональна разности фаз входных сигналов:

V гши — — 7, 1 где р — фазовый сдвиг входных сигналов;

Т вЂ” период следования широтных импуль25 сов.

Логическое уравнение получения широтных импульсов имеет вид:

456349

Предмет изобретения (2

Составитель А. Туляков

Техред Г. Васильева

Редактор Б. Федотов

Корректор А. Васильева

Заказ 517/16 Изд. 1 1з 287 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Ш иротные импульсы поступают на генераторы тока 8, 9, давая разрешение .на заряд

ынтегр ирующих конденсаторов 6, 7 постоянным током до напряжения, пропорционального длительности импульсов, т, е. разности фаз на входе. Знак рассогласования по фазе между сигналами а, а и b, Гопределяется компаратором 4 и выдается в блок 5 .и на первый выход дискри м инатора. Блок 5 формирует сипналы разряда конденсаторов 6, 7 в соответстви и с логическими уравнениями

Н,=т.х,+т х, Н,= — т.х +и х, а b где Н> и H> — сигналы разряда конденсаторов

6, 7; ти m — сигналы компаратора 4; х, и х; — специальные сигналы, формируемые в блоке 5 из сигналов а, а; хь и хь — специальные сигналы, формируемые в блоке 5 из сигналов о, b.

Таиим образом, разряд конденсаторов 6, 7 происходит от сигналов х и х, либо xb .и хГ, в зависимости от состояния компаратора 4, т. е. в зависимости от знака разности фаз на входе.

Сигналы разряда действуют на конденсаторы 6; 7 через разрядные устройства 10, 11.

Благодаря широтным ымпульсам и сигналам разряда обеспечивается двухтактная циклическая работа схемы. Разряд и заряд конденсатора 6 совершаются в тот полупериод рабочей частоты дискриминатора, когда конденсатор 7 запоминает постоянное напряжение, до кото5 рого он был заряжен в предыдущем полупериоде работы. При этом благодаря схеме 12 на втором выходе дискриминатора оказывается напряжение ко нденсатора 7. Во втором полупериоде конденсатор 7 заряжается, а кон10 денсатор 6 запоминает напряжение, до которого он был заряжен в предыдущий полупериод; при этом напряжение с конденсатора 6 поступает на выход дискриминатора.

Фазовый дискриминатор, содержащий блок преобразования разности фаз в широтный импульс, фазовый компаратор, источники вход20 ных напряжений и интегрирующие конденсаторы, отличающийся тем, что, с целью повышения его быстродействия, источники входных напряжений подключены к блоку преобразования разности фаз в широтный им25 пульс, к фазовому компаратору и к блоку сигналов разряда, соединенному также с фазовым компаратором, а интегрирующие конденсаторы подключены соответственно через генераторы тока к блоку преобразования разно30 сти фаз в широтный импульс, через разрядные устройства — к блоку сигнала разряда и к схеме выделения сигнала с большей амплитудой.