Устройство для определения моментов времени квантования сигнала

Иллюстрации

Показать всеРеферат

твСЕГ ""

ЛАЕТ»-.;

».» - о л;»

О П И С А Н И Е III) 45636I

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Савз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 16.03.73 (21) 1894883/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 05.01.75. Бюллетень № 1

Дата опубликования описания 11.03.75 (51)) М, Кл. Н 03k 13/02

Государственный комитет

Совета Министров СССР ло делам изобретений и открытий (53) УДК 681.34(088.8) (72) Авторы изобретения

Б. Я. Авдеев, Е. М. Антонюк и Е. И. Семенов (71) Заявитель

Ленинградский ордена Ленина электротехнический институт имени В. И. Ульянова (Ленина) (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОМЕНТОВ

ВРЕМЕНИ КВАНТОВАНИЯ СИГНАЛА (2) R, (t) = Лх (/) dt, о"

Изобретение относится к области измерительных информационных систем и может быть использовано, например, в телеметрии, системах связи и управления.

Известны устройства для определения моментов времени квантования сигнала, содержащие дифференцирующий, запоминающевычитающий блоки и схему. сравнения.

Недостатками таких устройств является налич ие сложного генератора гиперболическп изменяющегося напряжения и большой разброс погрешности апроксимации.

Целью изобретения является повышение точности,и упрощение устройства.

Эта цель достигается тем, что предложенное устройство содержит, интегратор, вход которого соединен с выходом запоминающе-вычитающего блока. Выход интегратора подключен к одному из входов схемы сравнения.

Другой вход схемы сравнения подключен к шине задания величины допустимой погрешности, а выход — ко входу сброса интегратора.

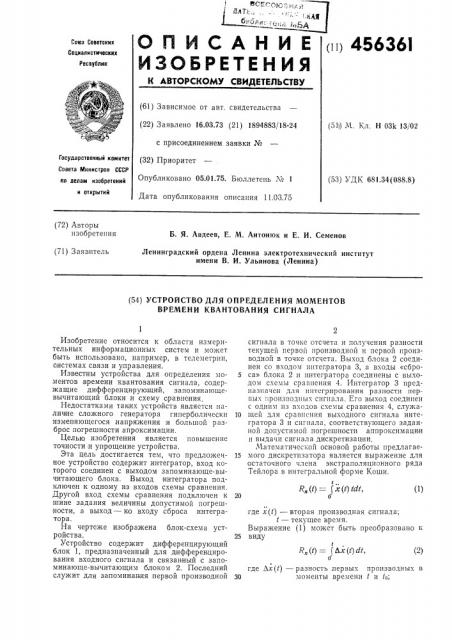

На чертеже изображена блок-схема устройства.

Устройство содержит дифференцирующий блок 1, предназначенный для д|ифференцирования входного сигнала и связанный с запоминающе-вычитающим блоком 2. Последний служит для запоминания первой производной сигнала в точке отсчета и получения разности текущей первой производной и первой производной в точке отсчета. Выход блока 2 соединен со входом интегратора 3, а входы «сбро5 са» блока 2 и интегратора соединены с выходом схемы сравнения 4. Интегратор 3 предназначен для интегрирования разности nepBI Ix производных сигнала, Его выход соединен с одним пз входов схемы сравнения 4, служаI0 щей для сравнения выходного сигнала интегратора 3 и сигнала, соответствующего заданной допустимой погрешности аппроксимации и выдачи сигнала дискретизации.

Математической основой работы предлагае15 мого дискретизатора является выражение для остаточного члена экстраполяционного ряда

Тейлора в интегральной форме Коши.

f ..

R„(t) =- jx(t) tdt, 20 о где x(t) — вторая производная сигнала;

1 — текущее время.

Выражение (1) может быть преобразовано и

25 виду где Лх(1) — разность первых производных в

30 моменты времени t и 4;

456361

Предмет изобретения

Составитель Г. Осипов

Корректор Л. Котова

Техред Г. Васильева

Редактор Л. Утехина

Заказ 517 18 Изд. № 287 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-зо, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

1в — момент начала интервала дискретизации.

Отсчет производится в случае, если R (t) =

=е„, где ед — заданная допустимая погрешность аппроксимации.

Входной сигнал поступает на дифференцирующий блок 1, на выходе которого появляется напряжение, пропорциональное первой производной входного сигнала. Это напряжение подается на блок 2, где происходит запоминание первой производной сигнала в начала интервала дискретизации (в точке отсчета) и вычисление разности между запомненным значением первой производной и текущим ее значением, Эта разность поступает на интегратор

3, где происходит интегрирование в соответствии с выражением (2).

Таким образом, в соответствии с выражением (2) блока 1, 2 и 3 вычисляют остаточный член экстраполяционного ряда Тейлора R>(t).

Схема сравнения 4 срабатывает, если сигнал на выходе интегратора 3 равен постоянному напряжению, соответствующему заданной погрешности аппроксимации вд. Одновременно с сигналом дискретизации с выхода схемы сравнения 4 подаются сигналы «сброса» на блок 2 и интегратор.

Устройство для определения моментов вре10,мени квантования сигнала, содержащее дифференцирующий блок, подключенный ко входу запоминающе-вычитающего блока, и схему сравнения, выход которой соединен с управляющим входом запоминающе-вычитающего

15 блока, о тл ич а ю щ ее с я тем, что, с целью повышения точности и упрощения устройства, оно содержит интегратор, вход которого соединен с выходом запоминающе-вычитающего блока, выход интегратора подключен к одно20 му из входов схемы сравнения; другой вход схемы сравнения подключен к шине задания величины допустимой погрешности, а выход— ко входу сброса интегратора.