Пересчетное устройство

Иллюстрации

Показать всеРеферат

Йи.союзная

О П И С А.Й:"И"Е

ИЗОБРЕТЕН ИЯ -т;"1 ц. 456367

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 19.04.72 (21) 1774192/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 05.01.75. Бюллетень № 1

Дата опубликования описания 20.02.75 (51) М. Кл. H 03k 23/00

Н 03k 21/00

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.374.32 (088.8) (72) Авторы изобретения (71 ) Заявитель

В. П. Волосников, Е. И. Войцех и А. В. Василенко

Днепропетровский химико-технологический институт им. Ф. Э. Дзержинского (54) ПЕР ЕСЧ ЕТНОЕ УСТРОЙСТВО

Изобретение относится к элементам промышленной электроники и может быть использовано при создании счетных или других цифровых схем.

Известно пересчетное устройство, содержащее триггер памяти и две схемы совпадения, выполненные на элементах «И — НЕ».

Целью изобретения является упрощение изменения коэффициента пересчета.

Для этого предлагаемое устройство содержит два диода и конденсаторы, причем выходы триггера памяти подключены через диоды к соответствующим входам схем совпадения и к одной обкладке конденсаторов, другая обкладка которых соединена с общей шиной.

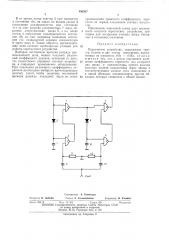

Структурная схема предлагаемого пересчетного устройства представлена на чертеже.

Оно содержит триггеры 1, 2 памяти, схемы

3, 4 совпадения, диоды 5, б, конденсаторы 7, 8 и две дифференцирующие цепочки состоящие из конденсаторов 9 и 10 и резисторов 11 и 12.

Обозначим условно ненасыщенное состояние схемы через «1», а насыщенное — через «О».

Рассмотрим работу схемы в счетном режиме.

На вход схемы 3, 4 совпадения подается серия импульсов положительной полярности, которые дифференцируются цепочками, состоящими из конденсаторов 9, 10 и резисторов

11 и 12. Подача импульса положительной полярности на вход любой из схем совпадения равноценно подаче на этот вход сигнала «1».

5 При подаче сигнала «1» на второй вход схемы 4 совпадения на ее выходе будет «1», так как по первому входу этой схемы действует «О», поступающий с выхода триггера 1, следовательно, изменение состояния триггеров

10 памяти не произойдет.

В случае подачи сигнала «1» на вход схемы

3 совпадения на ее выходе получим сигнал

«О», так как на обоих ее входах будет дейст15 вовать сигнал «1».

С выхода схемы 3 совпадения сигнал «О», поступая на вход триггера 1 памяти, вызывает появление «1» на его выходе, что приведет к появлению сигнала «О» на выходе

20 триггера 2 памяти. Поскольку выход триггера 2 соединен со входами триггера 1 и схемы

3 совпадения, то для того, чтобы обеспечить надежность срабатывания устройства между выходом триггера 2 и входом схемы 3 совпа25 дения включена времязадающая цепочка, состоящая из включенных последовательно диода 5 и конденсатора 7, между выходом триггера 1 и входом схемы 4 совпадения включена аналогичная цепочка, состоящая из диода

30 б и конденсатора 8.

456367

Предмет изобретения

Составитель Э. Гилинская

Техред А. Камышникова Корректор Н. Учакина

Редактор В. Дибобес

Заказ 285, 18 Изд. X 262 Тираж 901 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, К-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

В то время, когда триггер 2 уже находится в состоянии «0», на одном из входов схемы 3 совпадения поддерживается еще состояние

«1» за счет разряда конденсатора 7 через обратное сопротивление диода 5, а на входе схемы 4 совпадения поддерживается состояние «О» за счет задержки появления состояния «1» создаваемой зарядом конденсатора

8 через диод б. Таким образом, времязадающие цепи создают необходимые условия для работы пересчетного устройства.

Выбирая постоянную времени разряда времязадающей цепи, можно получить различный коэффициент деления, отличный от двух, что существенно упрощает счетные устройства, и сокращает применяемое оборудование.

При получении различного коэффициента пересчета необходимо выбирать времязадающую цепочку такой, чтобы величина постоянной времени разряда последней была не менее произведения принятого коэффициента пересчета на период следования счетных импульсов.

Применение описанной схемы дает возмож5 ность получить пересчетное устройство, пригодное для построения счетных декад, бинарных и кольцевых счетчиков, Пересчетное устройство, содержащее триггер памяти и две схемы совпадения, выполненные на элементах «И» — «НЕ», о тл и ч аю щ е е с я тем, что, с целью упрощения изме15 пения коэффициента пересчета, оно содержит два диода и конденсаторы, причем выходы триггера памяти подключены через диоды к соответствующим входам схем совпадения и к одной обкладке конденсаторов, другая об20 кладка которых соединена с общей шиной.