Устройство для испытания каналов связи

Иллюстрации

Показать всеРеферат

пп 456373

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К ABTOPCKOMY CBHPETEAbCTBY

Союз Советских

",оциалистических

Респуолик (61) Зависимое от авт. свидетельства (22) Заявлено 27.06.72 (21) 1801955/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 05.01.75. Бюллетень ¹ 1

Дата опубликования описания 20.02.75 (51) M. Кл. Н 041 1/14

Н 04! 11/08

Гасударственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.391.833 (088.8) (72) Авторы изобретения

А. И. Усачев и 3. М. Каневский

Воронежский политехнический институт (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИСПЫТАНИЯ КАНАЛОВ СВЯЗИ

Изобретение относится к электросвязи, может быть использовано для испытаний каналов связи с целью измерения их статических характеристик.

Известны устройства для испытания каналов связи, содержащие датчик случайной последовательности, подключенный к блоку задержки, один выход которого подключен к одному из входов блока сравнения, а другой через последовательно соединенные прямой и обратный каналы связи — к другому его входу.

Цель изобретения — раздельный подсчет ошибок в прямом и обратном каналах — достигается тем, что в предлагаемом устройстве между первым и дополнительными выходами блока задержки и блоком сравнения включен сумматор по модулю т (основание кода), а между выходом прямого канала и входом обратного канала включены последовательно соединенные дополнительные блок задержки и сумматор по модулю т,, причем выход блока сравнения через дешифратор подключен к анализаторам потоков ошибок прямого и обратного каналов.

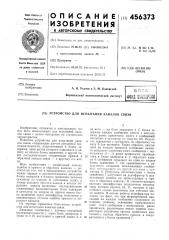

На чертеже приведена блок-схема устройства для испытания каналов связи.

Двоичные сообщения с датчика случайной последовательности 1 через блок задержки 2 (если т = 2) поступают в прямой канал 3, а из него — на блок задержки 4. С блока задержки каждое сообщение вместе с несколькими ранее принятыми (всего 3 сообщений) поступает в сумматор по модулю т5. Резуль5 тат передается с сумматора по обратному каналу 6 для проверки. Таким образом, квитанцией на каждое принятое сообщение является результат сложения этого сообщения с несколькими (t — 1) ранее принятыми, хранящи10 мися в блоке задержки 4. С обратного канала 6 сообщения попадают на один из входов блока сравнения 7, где сравниваются с результатом сложения неискаженных сообщений, поступающим на другой его вход с сум15 матора 8. Импульсы несоответствия с блока сравнения 7 поступают на дешифратор 9, разделяющий ошибки на происходящие в прямом и обратном каналах. К соответствующим выходам дешифратора подключены анализа20 торы потоков ошибок 10, 11, которые в простейшем случае выполнены как счетчики числа ошибок. В основу работы дешифратора положен тот факт, что при формировании квитанций на каждое сообщение сложением по

25 модулю, равному основанию применяемого кода, этого сообщения с несколькими ранее принятыми, различными видам ошибок соответствуют различные группы ошибочных квитанций с выхода обратного канала, а следо30 вательно и с блока сравнения 7.

456373

Составитель А. Туляков

Редактор Б. Федотов

Корректор Т. Хворова

Техред А. Камышникова

Заказ 278/14 Изд. Ме 263 Тираж 739 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, гК-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

Предмет изобретения

Устройство для испытания каналов связи, содержащее датчик случайной последовательности, подключенный к блоку задержки, один выход которого подключен к одному из входов блока сравнения, а другой через последовательно соединенные прямой и обратный каналы связи — к другому его входу, о т л и ч аю щ е е с я тем, что, с целью раздельного подсчета ошибок в прямом и обратном каналах, между первым и дополнительными выходами блока задержки и блоком сравнения включен сумматор по модулю т (основание кода), а между выходом прямого канала и входом обS ратного канала включены последовательно соединенные дополнительные блок задержки и сумматор по модулю т, причем выход блока сравнения через дешифратор подключен к анализаторам потоков ошибок прямого и об10 ратного каналов.