Интегральное запоминающее устройство на мдп транзисторах

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ т111 4580

Сова Советских

Социалистических

Респчолик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву. (22) Заявлено 19.07.73 (21) 1960796. 18-24 с присоединением заявки ¹ (23) Приоритет

Опубликовано 25.01.75. Бюллетень № 3

Дата опубликования описания 15.05.75 (51) М. Кл. G 1lс 11, 40

Государственный комитет

Совета 1Иинистров СССР (53) УДК 681.327 (088.8) по делам нзаоретений н открытий (72) Авторы изобретения

А. И. Мальцев, А. П. Нагин и В. В. Поспелов (71) Заявитель (54) ИНТЕГРАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

НА МДП-ТРАНЗИСТОРАХ

Изобретение относится к вычислительной технике.

Известно интегральное запоминающее устройство (ЗУ) на МДП-транзисторах, содержащее матрицу накопителя, каждая ячейка которой состоит из МДП-транзистора с изменяемым пороговым напряжением, и дешифраторы строк и столбцов.

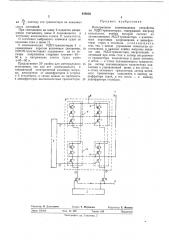

Предлагаемое ЗУ отличается тем, что в каждую ячейку матрицы введены два МДПтранзистора, нагрузочный и активный при этом сток и затвор нагрузочного транзистора подключены к шине питания, а исток— к стоку запоминающего транзистора, затвор запоминающего транзистора подключен к управляющей шине, а его исток — к стоку активного транзистора, затвор активного транзистора подключен к выходу дешифратора строк, а его исток — к выходу дешифратора столбцов.

На чертеже дана электрическая схема предлагаемого ЗУ.

Устройство состоит из матрицы накопителя

1, дешифратора строк 2, дешифратора столбцов 3, ячейки матрицы накопителя 4, запоминающего МДП-транзистора с изменяемым пороговым напряжением 5, нагрузочного

МДП-транзистора 6, активного МДП-транзистора 7, шины питания 8, управляющих шин

9, МДП-транзистора 10, выходной шины ЗУ

11, выходной шины дешифратора строк 12 и выходной шины дешифратора столбцов 13.

5 Для записи необходимого массива информации все запоминающие МДП-транзисторы

5 с изменяемым пороговым напряжением предварительно переводят в одно состояние (стирание). Для этого на шину 9 подают па10 пряжение стирания, а шины 8 и 11 заземляют. Затем избирательно МДП-транзисторы 5 переводят в другое состояние. Для этого на шину 9 подают напряжение записи Ез, обеспечивающее отпирание запоминающего МДП15 транзистора 5, а на шину 8 — напряжение, Еъ равное — + U,, где Уо — пороговое на2 пряжение нагрузочного МДП-транзистора 6.

Выходная шина 11 при этом заземлена.

Потенциал канала запоминающего транзистора в выбранной ячейке 4 будет близок нулю (это обеспечивается определенным соотношением сопротивлений каналов транзисто25 ров 6, 7 и 10), поэтому состояние транзистора изменится.

У всех остальных запоминающих МДПтранзисторов 5 каналы будут иметь потенци458036

Редактор Н, Данилович

Заказ 1161/4

Техред T. Миронова

Корректор Е, Мохова

Подписное

Изд. № 508

Тираж 648

Типография, пр. Сапунова, 2 ал —, поэтому эти транзисторы не изменяюг

Ез г своих состояний.

При считывании на шину 9 подается напряжение считывания, шина 8 подключается к источнику напряжения, а шина 11 заземляется.

О состоянии выбранного элемента судят по величине тока в шине 11.

У запоминающих МДП-транзисторов 5 с изменяемым порогом включения (например, МНОП-транзисторов) подаваемое на их затворы напряжение стирания составит 40—

50 в, а напряжение записи будет равно

+40 — 50 в.

Предлагаемое ЗУ удобно для интегрального исполнения, так как нет необходимости в специальной электрической изоляции матрицы накопителя от дешифраторов 2 (строк) и 3 (столбцов), а также можно не применять в дешифраторах высоковольтные транзисторы.

Предмет изобретения

Интегральное запоминающее устройство на МДП-транзисторах, содержащее матрицу

5 накопителя, ячейка которой состоит из запоминающего МДП-транзистора с изменяемым пороговым напряжением, и дешифраторы строк и столбцов, отличающееся тем, что, с целью упрощения технологии из10 готовления, в каждую ячейку матрицы введены два МДП-транзистора, нагрузочный и активный при этом сток и затвор нагрузочного транзистора подключены к шине питания, а исток — к стоку запоминающего транзисто15 ра, затвор запоминающего транзистора подключен к управляющей шине, а его исток— к стоку активного транзистора, затвор активного транзистора подключен к выходу дешифратора строк, а его исток — к выходу

20 дешифратора столбцов.