Многофункциональное запоминающее устройство

Иллюстрации

Показать всеРеферат

11тГ-ТИ11м бибамотена Ь1ЬА

ОПИСАНИЕ

ИЗО6РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< ц 458037

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 25.04.72 (21) 1777942/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 25.01.75. Бюллетень № 3

Дата опубликования описания 02,04.75 (51) М. Кл. б 1lс 15/00

Государственный комитет.Совета Ииннстров СССР ло делам изобретений и открытий (53) УДК 628 327 66 (088.8) (72) Авторы изобретения (71) Заявитель

Е. П. Балашов и Ц1. Д. Да д

Ленинградский ордена Ленина электротехнический институт им. В, И. Ульянова (Ленина) (54) МНОГОФУНКЦИОНАЛЬНОЕ ЗАПОМИНАЮ1ЦЕЕ

УСТРОЙСТВО

Изобретение относится к вычислительной технике.

Системы переработки информации получают все более широкое применение для решения информационно-логических задач во многих областях науки и техники.

Процесс интегрирования является одной из этих задач. В режиме интегрирования различаются три операции: операция подсчета единичных приращений, операция суммирования двух слов и операция определения переполнения интегратора, поэтому каждая система, в которой выполняется процесс интегрирования, должна содержать счетчик, сумматоры, дискриминатор и три регистра — регистр подынтегральной переменной 1", регистр суммы R u регистр переполнения ЛХ.

Использование запоминающего устройства (ЗУ) для переработки информации позволяет значительно улучшить характеристики интегрирующих систем. При этом количество передач внутри интегрирующей системы сокращается.

Известны вычислительные машины, в которых операции суммирования двух слов выполняются в ЗУ. Однако им свойственна сложность накопителя и зависимость времени выполнения операций от значений разрядов суммируемых кодов, Известны схемы для реализации сложных логических функций с числами, хранящимися на магнитных сердечниках. Для выполнения сложных логических функций, например, опе5 рации суммирования или вычитания двух слов, на основе элементарных логических операций «ИЛИ» и «ШТРИХ ШЕФФЕРА» информация предварительно считывается из ячейки ЗУ в промежуточный накопитель и пе1о резаписывается в ту же ячейку. При этом используются возникающие при записи на выходе запоминающей ячейки сигналы.

Таким образом, логические операции выполняются фактически вне ЗУ на специаль15 ных схемах.

Известно логическое запоминающее устройство, содержащее накопитель на числовых линейках с адресными и разрядными шинами, подключенными через адресные и разрядные

20 вентили к соответствующим входам адресных и разрядных формирователей, шину считывания, подключенную к входу усилителя считывания, выход которого соединен с входом входного триггера и блок управления.

25 Цель изобретения — расширение логических возможностей запоминающего устройства.

В предлагаемом многофункциональном запоминающем устройстве (МФЗУ) можно реализовать процесс интегрирования, т. е, мож30 но реализовать операцию суммирования еди458037 ничных приращений, операцию суммирования или вычитания двух слов, в зависимости от знака и абсолютной величины приращения независимой переменной, и операцию определения переполнения.

Поставленная цель достигается путем введения в ЗУ управляющих вентилей, одпи из входов которых подключены к соответствующему выходу блока управления, вторые через разрядные вентили к соответствующим входам разрядных формирователей и схемы фиксации приращений, вход которой соединен с выходом усилителя считывания, выходы схемы фиксации приращений соединены соответственно с входами входного триггера и блока управления, и выполнением числовых линеек в виде двух счетчиков Т-счетчика и R-счетчика.

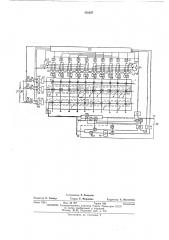

На чертеже приведена функциональная схема предлагаемого МФЗУ.

МФЗУ содержит накопитель 1 с числовыми линейками 2, каждая из которых является интегратором, включающим счетчик 3, элементы 4 памяти, хранящие значение переменной Ъ", элемент 5 памяти для хранения знака переменной У, элемент 6 памяти для хранения знака программы и К-счетчик 7, элементы 8 памяти, хранящие значение R, элемент 9 памяти для хранения значения переполнения, элемент 10 памяти для хранения знака переполнения. Кроме того, схема ЗУ содержит адресные шины 11, разрядные шины 12, шину

13 считывания, усилитель 14 считывания, выход 15 которого подключен на нулевой вход входного триггера 16 через общий вход 17

МФЗУ, управляющие вентили 18, схему HE

19, блок управления 20, который обеспечивает последовательное срабатывание разрядных ключей 21 и вырабатывает управляющие сигналы, поступающие на другие блоки устройства, разрядные вентили 22, разрядные формирователи 23, управляющие вентили 21 счетчика, управляющие вентили 25 R-счетчика, схему фиксации приращения 26, в состав которой входят триггер 27 фиксацпи знака приращения, промежуточный триггер 28, триггер 29 фиксации начального импульса, вентили 30 — 32, схема НЕ 33, линия задержки

34, шина 35 сброса, шины 36 номера интеграторов, шины ЗУ набора адресов 37, управляющие вентили 38, адресные схемы 39 ИЛИ, адресные вентили 40, адресные формирователи 41, шину 42 выборки Т-счетчика, шину 43 выборки R-счетчика, шины 44 — 49 управления.

Блок управления 20 состоит из задающего генератора и разрядного распределителя.

Схема МФЗУ работает следующим образом.

При подаче на шины 36 сигнала выборки соответствующий интегратор 2 начинает работать в режиме интегрирования. В режиме интегрирования различаются две стадии.

В первой стадии ЗУ работает как Т-счетчик для расчета величины текущего значения

1*(1* = Т+;» Д 1" J

1 в соответствии с принципами подсчета единичных приращений. Вместо определения значения g Л 1 отдельным счетчиком и nol следующего суммирования результатов с содержимым Т-регистра, в предлагаемом устройстге используется Т-c÷åò÷èê 3, на общий вход 17 МФЗУ ЛТ, импульсы подаются непосредственно, и содержимое которого хра10 нится на элементах памяти 4 представляет значение Т. Для этого в каждом цикле на тактах 4 и 4 сигнал на управляющей шине

43 равен «1» и сигнал на шипе 42 равен «О», а начиная с такта 4 до конца цикла, сигнал

15 на шине 43 равен «О» и сигнал на шине 42 равен «1». В -ом цикле и на такте 4 система с помощью управляющих сигналов на шинах

48 — 49 и сигналов на шинах 37 выбора адресов читает значение приращения ЛТ,, которое подается на хранение на входной триггер

16 с помощью сигнала на шине 44. На такте

1 система считает знак приращения ЛТ,, который подается для запоминания на промежуточный триггер 28. Начало процесса суммпро25 вания значений приращений определяется положением начального импульса в Y-счетчике.

JIо прихода начального импульса на нулевых выходах триггера 29 фиксации начального импульса и триггера 27 фиксации знака прира30 щения появляется «1», вследствие чего система работает только в режиме считывания и в режиме записи. Когда начальный импульс подается на единичный вход триггера 29 фиксации начального импульса, на единичном вы35 ходе этого триггера появляется «1», открывая управляющие вентили 18 и 3::.

Процесс суммирования приращения AY ; должен начинаться после окончания действия начального импульса. Для этого в цепь вен40 тильной схемы 31 включена линия задержки

34. В результате этого знак приращения ЛГ; подается для запоминания ца три rcp 27 фиксации знака приращения, и система начинает работат как Y-счетчик, суммируя (вычитая)

45 значения приращения ЛТ; г содержимым 1счетчика. Если знак приращения М", равен

«1», т. е. положителен, то на единичном выходе триггера 27 фиксации знака приращения появляется «1» и счетчик работает в режиме

50 суммирования, а если знак приращения ЛЪ; равен «О», то на нулевом выходе триггера 27 фиксации знака приращения появляется «1» и счетчик работает в режиме вычитания. В момент окончания суммирования илп вычитания

55 приращения ЛТ„триггер 27 фиксации знака приращения, промежуточный триггер 28 и триггер 29 фиксации начального импульса переходят в нулевое состояние с помощью сигнала сброса на шине 35 и сигнала на шине

60 46, чем осуществляется подготовка к началу следующего цикла.

В последнем цикле этой стадии работы

МФЗУ на тактах 4 и t считываются значение и знак Лх, которые сохраняются в схеме

65 26 фиксации приращения на время второй ста458037 дии работы ЗУ, в том же цикле знак Лх записывается в последнем разряде элемента памяти 10 R-счетчика интегратора.

Таким образом, схема 26 фиксации приращения в этой стадии выполняет функцию ЛХумножителя, так на единичном выходе триггера 27 фиксации знака приращения появляется «1», в результате чего система работает в режиме суммирования на все время второй стадии при ЛХ= + 1, на нулевом выходе триггера 27 фиксации знака приращения появляется «1», в результате чего система работает в режиме вычитания на все время второй стадии, при bX= — 1, а при ЛХ=О цикл интегрирования заканчивается, Во второй стадии ЗУ работает как R-счетчик для суммирования содержимого Т-счетчика к содержимому R-счетчика для получения величины

R* = R+ rhX, Процесс суммирования двух слов, содержащихся в Х- и R-счетчиках 4 и 8, происходит непосредственно в R-счетчике без перевода разрядов К-слова в соответствующее число импульсов. Это осуществляется при помощи блока управления 20 и управляющих сигналов на шинах 41 — 44.

В i-ом цикле с момента 4 до 4 i сигналы на шинах 43 — 44 равны «О», т. е. система заблокирована. На такте 1; и при поступлении сигнала на шину 42 и управляющих сигналов на вентили 25 К-счетчика на входном триггере 16 появляется значение i-ro разряда Ъ"счетчика 1 ;, В интервале t„ < и до конца цикла сигнал на шине 43 равен «1» и сигнал на шине 42 равен «О». Система при этом работает как R-счетчик, суммируя (вычитая) значения

1"; с содержимым R-счетчика.

Значение ЛЛ определяется переполнением последнего разряда R-счетчика. Определяет5 ся знак ЛЛ в последних двух циклах, когда суммируются знак Т, хранящийся на элементе памяти 5 и знак программы со знаком ЬХ, хранящимся на элементе памяти 10, который был записан в этом разряде в кош:,с первой

10 стадии работы ЗУ.

Предмет изобретения

1. Многофункциональное запоминающее уст15 ройство, содержащее накопитель на числовых линейках с адресными и разряднымн шинамн, подключенными через адресные и разрядные вентили к соответствующим входам адресных и разрядных формирователей, шину считыва20 ния, подключенную ко входу усилителя считывания, выход которого соединен со входом входного триггера и блок управления, о т л ич а ю щ е е с я тем, что, с целью расширения логических возможностей устройства, в него

25 введены управляющие вентили, одни из входов которых подключены к соответствующему выходу блока управления, вторые — через разрядные вентили к соответствующим входам разрядных формирователей, и схема фик30 сации приращений, вход которой соединен с выходом усилителя считывания, выходы схемы фиксации приращений соединены соответственно с входами входного триггера и блока управления.

35 2. Устройство по п. 1, отличающееся тем, что числовые линейки выполнены в виде двух счетчиков

458037

Составитель Е. Балашов

Техред Т. Миронова

Редактор E. Гончар

Корректор А. Васильева

Типография. пр. Сапунова, 2

Заказ 728/1 Изд. № 397 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-35, Раушская наб., д. 4/5