Реверсивный счетчик

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (и) 458 100

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свидетельству (22) Заявлено 12.04.73 (21) 1905845/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 25.01.75. Бюллетень № 3

Дата опубликования описания 10.03.75 (5)) М. Кл, Н 03k 23/02

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.374.22 (088.8) (72) Автор изобретения

В. А. Грехнев (71) Заявитель (54) РЕВЕРСИВНЫЙ СЧЕТЧИК

Изобретение относится к вычислительной технике и предназначсно для суммирования или вычитания последовательности входных им пульсов.

Известен реверсивный счетчик, каждый разряд которого выполнен на счетном триггере, состоящем из триггера памяти, коммутационного триггера и трех схем И вЂ” НЕ, причем единичный выход триггера памяти соединен с нулевым входом коммутационного триггера, единичный выход коммутационного триггера соединен с нулевым входом триггера памяти, а нулевой выход коммутационного триггера соединен с входом второй схемы И вЂ”,НЕ, выход которой соединен с входом третьей схемы

И вЂ” HE, выход третьей схемы И вЂ” НЕ соединен с входом впервой схемы И вЂ” HE и с единичным входом триггера памяти. Кроме тото, нулевой выход коммутационного триггера соединен со схемой И вЂ”.НЕ управления вычитанием, выход которой соединен с нулевым и единичным входами коммутационного трипгера последующего старшего разряда, а выход второй схемы И вЂ” HE данного разряда соединен с входом схемы И вЂ” НЕ у правления сло>кением, выход которой соединен с входами первой и третьей схем И вЂ” НЕ последующего старшего разряда.

Целью изобретения является повышение быстродействия.

Для этого выход единичного плеча коммутационного триггера и выход первой схемы И—

HE соединены с входами схемы И вЂ” НЕ управления сложением.

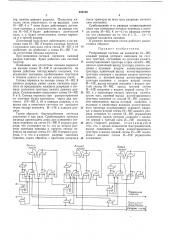

5 На чертеже ариведена блок-схема счетчика.

Реверсивный счетчик содержит схемы И—

HE 1 и 2, образующие триггер памяти, схемы

И вЂ” НЕ 3 и 4, образующие коммутационный триггер, схемы И вЂ” HE 5, б, 7, образующие со10 ответственно, первую, вторую и третью схемы

И вЂ” НЕ. Схемы И вЂ” НЕ 8 образуют схемы управления сложением, а схемы И вЂ” НЕ 9— схемы управления вычитанием.

Счетчик работает следующим образом, 15 B режиме суммирования на входы схем И—

НЕ 8 поступают сигналы, равные логической единице, а на входы схем И вЂ” НЕ 9 — сигналы, равные логическому нулю.

Первый разряд счетчика работает, как

20 обычный триггер со счетным входом. Поскольку на выходе схем И вЂ” НЕ 9 сигнал равен логической единице, срабатывание второго разряда осуществляется лишь при поступлении сигнала |переноса с выхода.

25 Схема И вЂ” HE 8 первого разряда содержит единицу. Если сигнал переноса отсутствует, т. е. если он равен логическому нулю, то на выходе схемы И вЂ” HE " второго разряда логическая единица будет действовать незавпси30 мо от того, в каком состоянии находится триг458100

TpE ///(///

pexpюо

ЮерЯ ы гер памяти данного разряда. Поскольку импульс счета отсутствует, то на выходах схем

И вЂ” HE 4 и 7 тоже будет действовать логическая единица, а следовательно, на выходе схемы И вЂ” НЕ 8 будет действовать логический нуль, т. е. будет отсутствовать сигнал переноса и в третий разряд.

Логический нуль будет действовать и на выходах схем И†HE 3 второго разряда, поэтому с приходом импульса счета схема И вЂ” НЕ 4 не сработает, не сработает и схема И вЂ” НЕ 7 изза отсутствия сигнала переноса.

При появлении сигнала переноса каждый разряд счетчика будет работать как счетный триггер.

Появление или отсутствие сигнала, переноса на выходе схемы И НЕ 8 запоминается на время действия тактирующего импульса, что исключает повторное срабатывание триггеров в течение одного и того же импульса счета.

Сигнал переноса на выходе схемы И вЂ” НЕ 8 данного разряда равен сумме сигналов переноса из:предыдущих младших разрядов и сигнала состояния триггера памяти данного разряда. Суммирова ние выполняют схемы И вЂ” НЕ

5 и 8. Сигнал переноса при распространении

:no счетчику будет проходить через два элемента (И вЂ” НЕ 5, 8) в каждом разряде, в то время как в известном счетчике он проходит через четыре элемента И вЂ” НЕ в каждом разряде.

Таким образом, быстродействие счетчика увеличено в два раза. Срабатывание третьего разряда происходить лишь,при появлении сигнала переноса на схеме И вЂ”,НЕ 8 второго разряда, что указывает на то, что во втором разряде записана единица и имеется сигнал переноса на выходе схемы И вЂ” НЕ 8 первого разряда, т. е. что и в первом разряде записана единица, таким образом, с приходом импульса счета триггеры во всех трех разрядах изменят свое состояние.

Срабатывание и-ro разряда осуществляется лишь при появлении сигнала переноса с выхода схемы И вЂ” НЕ 8 (и — 1)-го разряда счетчика, что указывает на то, что в 1, 2,... (n — 1) разряде находится единица.

В режиме вычитания схема работает аналогичным образом.

Предмет изобретения

Реверсивный счетчик на элементах И вЂ” НЕ, каждый разряд которого выполнен на счетном триггере, состоящем из триггера памяти, 15 коммутационного триггера и трех схем И вЂ” НЕ, причем единичный выход триггера памяти соединен с нулевым входом коммутационного триггера, единичный выход коммутационного триггера соединен с нулевым входом триггера

20 памяти, а нулевой выход коммутационного триггера соединен с входом второй схемы

И вЂ” НЕ, выход которой соединен с входом третьей схемы И вЂ” НЕ, выход третьей схемы

И вЂ” НЕ соединен с входом первой схемы И—

25 НЕ и с единичным входом трипгера памяти, кроме того, нулевой выход коммутационного триггера соединен со схемой И вЂ” НЕ управления вычитанием, выход которой соединен с нулевым и единичным входами коммутацион30 ного триггера последующего старшего разряда, а выход второй схемы И вЂ” HE данного разряда соединен со схемой И вЂ” HE управления сложением, выход которой соединен с входами первой и третьей схем И вЂ” НЕ последую35 щего старшего разряда, отличающийся тем, что, с целью повышения быстродействия. выход единичного плеча коммутационного триггера и выход первой схемы И вЂ” НЕ соединены с входами схемы И вЂ” HE у правления

40 сложением.