Устройство для цикловой синхронизации

Иллюстрации

Показать всеРеферат

" е °,. тоэча

Ф-, тт@@ (и) 459795

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Сиоз Советских

Социалистических

Респчблик (61) Зависимое от авт. свидетельства (22) Заявлено 16.02.73 (21) 1884315/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 05.02.75. Бюллетень № 5

Дата опубликования описания 02.06.75,Г (51) M. Кл. G 08с 19/28

Государственный комитет

Совета Министров СССР (53) УДК 621.398:654.94 (088.8) по делам изобретений н открытий (72) Автор изобретения

И. Ф. Хомич (71) Заявитель Филиал Пензенского политехнического института — Пензенский завод

ВТУЗ при заводе вычислительных электронных машин (54) УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

Предложенное устройство относится к технике передачи дискретной информации и

rrpeдназпачепо для использования в системах передачи данных циклическими кодами.

Известны устройства для ппкловой синхронизации, содержащие генератор тактовых импульсов, вход которого подключен к выходу блока тактовой подстройки, а выход через управитель — ко входу делителя частоты, блок деления на образующий многочлен, сигнальный вход которого соединен со входом блока тактовой подстройки, а вход сброса— с выходом делителя частоты.

Однако, при применении известных устройств в системах передачи данных, особенно при наличии радиоканалов с неравномерным распределением сбоев цикловой синхронизации, время вхождения в синхронизм весьма значительно.

ПредЛоженное устройство отличается тем, что в него введен блок памяти, содержащий последовательно соединенные счетчик импульсов и кодопреобразователь. Счетные входы счетчика импульсов, кодопреобразователя и управителя подключены к выходу делителя частоты, вход сброса счетчика импульсов соединен с выходом блока деления на образующий многочлен, а выход кодопреобразователя подключен к сигнальному выходу управителя.

Это позволяет существенно снизить время синхронизации и тем самым сократить потери пнформацип при приеме.

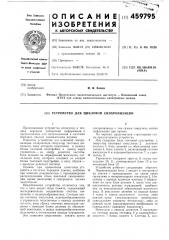

На чертеже представлена структурная схема предлагаемого устройства.

Оно содержит блок тактовой подстройки 1, генератор тактовых импульсов 2, делитель частоты 3, блок деления на образующий многочлен 4, блок памяти 5, включающий счетчик импульсов 6 и кодопреобразователь 7, и упра10 витель 8.

Управитель содержит триггер 9, схемы совпадения 10, 11, суммирующий блок 12 и вычитаюшнй блок 13.

Устройство работает следующим образом.

15 Первоначально блок 1 входит в синхронизм по тактам с приходящими пз линии связи сигналами и синхронизирует генератор 2. Импульсы с выхода делителя частоты 3 сбрасывают на нуль блок деления 4, после чего осу20 ществляется деление а-разрядной комбинации па определенный образующий многочлеп кода. В результате деления па выходе блока

4 через и тактов получается остаток либо равный нулю (анализируемая комбинация

25 принадлежит кодовому множеству), либо не равный нулю (анализируемая комбинация»е принадлежит кодовому множеству).

Импульсы с выхода делителя 3 поступают па счетные входы счетчика 6 и кодопреобра30 зователя 7 блока памяти 5. Счетчик 6, под459795 (J

Составитель Л. Морозов

Техрсд В. Рыоакова корректор Е. Мохова

Редактор Л. Утехина

Заказ 1260/10 Изд "о 5,9 Тираж 679 Подписное

Ц1-1ИИПИ Государственного ком «ста Совета Министров СССР по делам изобретений и открытий

Москва, 7Ê-35, Раушская наб., д. 4j5

Типография, пр. Сапунова, 2 считывающий фазовые сдвиги, первоначально был установлен в нулевое состояние импульсом с выхода блока 4. Если B результате последующего анализа п-разрядной комбинации в блоке 4 она не делится без остатка на образующий многочлен, то на счетный вход счетчика 6 поступает следующий импульс с выхода делителя 3, который одновременно сосчитает с кодопреобразователя 7 предшествующее значение счетчика 6. Кодопреобразователь 7 служит для выработки ряда последовательных импульсов, соответствующих числу импульсов, накопленных в счетчике 6 и предназначенных для «торможения» или «опережения» делителя 3. С этой целью управитель 8 с помощью триггера 9 и схем совпадения 10, 11 попеременно подключает выход кодопреобразователя 7 к блокам 12 и

13, расположенным в цепи между генератором 2 и делителем 3. В результате обеспечения последовательный режим поиска с анализом фазовых сдвигов до наступления синхронного, что соответствует делению п-разрядной кодовой комбинации на образующий многочлен без остатка. В последнем случае на выходе блока 4 появляется импульс, сбрасывающий счетчик 6 в нулевое состояние и запрещающий дальнейший режим поиска.

Таким образом, в предложенном устройстве в первую очередь анализируются те циклические сдвиги делителя 3, которые имеют наибольшую вероятность быть синхронными, т. е. реализуется оптимальный режим поиска, В результате сокращается число шагов до нахождения синхронного положения и, следовательно, уменьщается время вхождения в синхронизм по циклам.

Предмет изобретения

Устройство для цикловой синхронизации, содержащее генератор тактовых импульсов, вход которого подключен к выходу блока тактовой подстройки, а выход через управиГ5 тель — ко входу делителя частоты, блок деления на образующий многочлен, сигнальный вход которого соединен со входом блока тактовой подстройки, а вход сброса — с выходом делителя частоты, о т л и ч а ю щ е е с я тем, 20 что, с целью повышения быстродействия устройства, в него введен блок памяти, содержащий последовательно соединенные счетчик импульсов и кодопреобразователь; причем счетные входы счетчика импульсов, кодопре25 образователя и управителя подключены к выходу делителя частоты; вход сброса счетчика импульсов соединен с выходом блока деления на образующий многочлен, а выход кодопреобразователя подключен к сигналь30 ному выходу управителя.