Запоминающее устройство

Иллюстрации

Показать всеРеферат

о л, о о очей

О П И С A Н И E 459800

ИЗОБРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублик (61) Зависимое от авт. свидетельства (22) Заявлено 30.07.73 (21) 1955090 18-24 (51) М. Кл. G 1lс 11 00 с присоединением заявки №

Государственный комитет

Совета Министров СССР (32) Приоритет

Опубликовано 05.02.75. Бюллетень № 5

Дата опубликования описания 23.05.75 (53) УДК .681.327.6 (088.8) 0о делам изобретений и открытий (72) Авторы изобретения

В. П. Буйко и Г. В. Милославский (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение может быть использовано в качестве буферного запоминающего устройства.

Известно запоминающее устройство (ЗУ), содержащее входной регистр, выходы которого подключены к одним входам схем «И» первой группы, выходы которых соединены со входами запоминающего регистра, вторую группу схем «И», первые, входы которой подключены к выходам запоминающего регистра, третью группу схем «И» и блок управления.

Недостатками известного устройства являются невысокое быстродействие и сложность конструкции.

Описываемое устройство отличается от известного тем, что оно содержит сдвигающий регистр, входы которого подключены к выхо-. дам блока управления, выходы, кроме последнего — к другим входам схем «И» первой группы, последний выход — ко вторым входам схем «И» второй группы и первым входам схем «И» третьей группы, вторые входы которой соединены с выходами входного регистра, а выходы — с выходными шинами устройства.

Это позволяет упростить устройство и повысить его быстродействие.

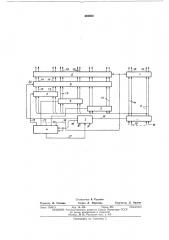

На чертеже изображена блок-схема ЗУ.

Устройство содержит входной m-разрядный регистр 1, блок управления 2, первую группу схем «И» 3, состоящую пз и — 1 подгрупп (каждая из которых включает m схем

5 «И»), сдвигающий регистр 4, запоминающий регистр 5, вторую группу схем «И» 6 (из (и — I) т схем «И») и третью группу схем

«И» 7 (из т схем «И»).

Первый 8 и второй 9 входы блока управле10 ния 2 являются соответственно первым и вторым входами ЗУ, а информационные входы

10 входного регистра 1 — информационными входами ЗУ, Информационные выходы 11 входного регистра 1 соединены соответствен15 но с первыми входами первой группы схем

«И» 3, вторые входы 12 которых в каждой подгруппе объединены и подключены соответственно к выходам, кроме последнего, сдвигающего регистра 4. Выходы 13 всех

20 схем «И» 3 соединены с входами запоминающего регистра 5, выходы 14 которого связаны с первыми входами схем «И» 6. Выходы

15 схем «И» 6 и 7 являются соответственно информационными выходами ЗУ. Последний выход 16 и-ro разряда сдвигающего регистра

4 соединен с объединенными вторыми входами схем «И» 6 и первыми входами схем «И»

7, вход шины сдвига 17 —.с первым выходом блока управления 2, а шина установки 18

30 (n — 1)-и разрядов в нуль и а-го разряда в

459800

3 единицу — со вторым выходом блока управления. Третий 19 и четвертый 20 выходы блока управления соединены соответственно с ши|нами установки в нуль входного 1 и запоминающего 5 регистров. Выходы 11 регистра 1 соединены также со вторыми входами третьей труппы схем «И» 7.

Устройство работает следующим образом.

В исходном состоянии при поступлении на устройство импульс начала записи блока управления 2 устанавливает сдвигающий регистр 4 в исходное состояние, характеризующееся нулевым состоянием первых (n — 1) -х его разрядов и единичным состоянием последнего, и-ro разряда, а также устанавливает в нулевое состояние входной 1 и запоминающий 5,регистры. Так как регистры 1 и

5 находятся в нулевом состоянии, то, несмотря на то, что на вторых входах схем «И» 6 имеется разрешающий уровень напряжения с и-го разряда сдвигающего регистра 4, все схемы «И» 6 и 7 закрыты. Все схемы «И» 3 также закрыты запрещающими уровнями напряжений с первых (n — 1)-х разрядов сдвигающего регистра 4. Регистр 4 соединен обратными связями, т. е. при сдвигах сигнал переноса из и-го разряда поступает на вход первого разряда. Поэтому, если в какой-либо разряд регистра 4 записана единица, то она непрерывно в кольце циркулирует по всем разрядам этого регистра.

В режиме записи в ЗУ каждой кодовой входной посылке предшествует импульс разрешения записи кодовой посылки. Поэтому перед приходом первой кодовой посылки импульс разрешения записи через блок управления 2 производит перенос единицы из и-го разряда регистра 4 в первый разряд, что приводит к тому, что первая кодовая посылка через регистр 1 и первую подгруппу схем

«И» 3 записывается в первые m разрядов регистра 5. Следующая кодовая посылка записывается во вторые т разрядов регистра

5, так как по импульсу разрешения записи второй кодовой посылки единица из первого разряда регистра 4 переносится в его второй разряд, Запись последующих кодовых посылок до (n — 1)-го включительно производится аналогично. B результате во всех ((n— — 1) Xm)-х разрядах регистра 5 будет записано и — 1 кодовых посылок. В и-ом такте по и-му импульсу разрешения записи и-й кодовой посылки единица из (и — 1)-го разряда

1р регистра 4 переписывается в и-й разряд.

В результате открываются по вторым входам все схемы «И» 6 и 7, и все (и — 1)-е кодовые посылки из регистра 5 и и-я кодовая посылка из регистра 1 выдаются на информа15 ционные выходы устройства 15.

В процессе работы устройства после каждой записи кодовой посылки в регистр 5 регистр 7 устанавливается в нуль, а после каждого и-го такта устанавливается в нуль

2р регистр 5.

В дальнейшем цикл работы ЗУ повторяется.

Предмет изобретения

Запоминающее устройство, содержа|цее входной регистр, выходы которого подключены к одним .входам схем «И» первой группы, выходы которых соединены со входами запозр минающего регистра, вторую группу схем

«И», первые входы которой подключены к выходам запоминающего регистра, третью группу схем «И» и блок управления, отл ич а ю щ е е с я тем, что, с целью упрощения устройства и повышения. его быстродействия, оно содержит сдвигающий регистр, входы которого подключены к выходам блока управления, выходы, кроме последнего, — к другим входам схем «И» первой группы, последний

4р выход — ко вторым входам схем «И» второй группы и первым входам схем «И» третьей группы, вторые входы которой соединены с выходами входного регистра, а выходы — с выходными шинами устройства.

Составитель В. Рудаков

Техред Л. Морозова

Редактор Л. Утехина

Корректор Л, Орлова

Заказ 1169/11 Изд. № 456 Тираж 651 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2