Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

ОПИСАН Е

ИЗОБРЕТЕНИЯ пп 45984I

Сонэ Советскик

Социалистических

Ресвублик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Зависимое от авт. свидетельства (22) Заявлено 27.10.72 (2!) 1841187/26-9 с присоединением заявки № (32) Приоритет

Опубликовано 05.02.75. Бюллетень ¹ 5

Дата опубликования описания 24.03.75 (51) Ч. Кл. H 03f 3/34

Государственный комитет

Совета Министров СССР

Il0 делам изобретений и открытий (53) УДК 621.375.024 (088.8) (72) Авторы изобретения В. И. Анисимов, М. В. Капитонов, Н. Н. Прокопенко и Ю. М, Соколов (71) Заявитель

Ленинградский ордена Ленина электротехнический институт имени В. И. Ульянова (Ленина) (54) ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ

Изобретение относится к радиотехнике и может быть использовано в операционных усилителях различного назначения.

Известны схемы дифференциальных усилителей, содержащие входной бал ансный каскад на транзисторах, включенных по схеме с общим коллектором, предварительный балансный каскад на транзисторах, включенных по схеме с общим эмиттером, и выходной балансный каскад на транзисторах с резистивным делителем в его общей эмиттерной цепи, к средней точке которого подключены базы транзисторов генераторов тока, причем коллекторы транзисторов генераторов тока связаны с эмиттерами транзисторов входного и предварительного каскадов.

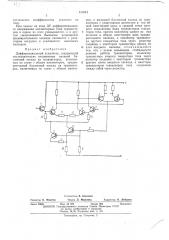

Цель изобретения — повышение стабильности режима работы транзисторов — достигается тем, что в предлагаемом дифференциальном усилителе коллектор транзистора второго генератора тока через резистор соединен с эмиттером транзистора другого плеча входного каскада, а эмиттеры транзисторов генераторов тока соединены между собой через резистор.

Принципиальная схема усилителя изобра1кена на чертеже.

Дифференциальный усилитель состоит из входного каскада на транзисторах 1 и 2, предварительного каскада на транзисторах 3 и 4 и входного каскада на транзисторах 5 и 6.

Эмиттеры транзисторов 5 и 6 связаны с делителем напряжения на резисторах 7 и 8, к средней точке которого подключены базы

5 транзисторов 9 и 10 генераторов тока. Коллектор транзистора 10 подключен к общей эмиттерной цепи предварительного каскада— резисторам 11 и 12, а коллектор транзистора

9 связан с каждым нз плеч входного каскаI0 да через резисторы 13 и 14. Эмиттеры транзисторов 9 и 10 объединены через резистор

15, а эмиттер транзистора 10 подключен к источнику питания через резистор 16.

Отношение коллекторных токов транзнсто15 ров 9 и 10 экспоненцнально зависит от сопротивления резистора 15. Это позволяет независимо от напряжения на базе транзистора

10 и требований к стабильности его коллекторного тока задавать микроамперный режим

20 входных транзисторов 1 и 2 с помощью небольшого по номиналу резистора 15. Под действием температуры напряжения на эмиттерно-базовых переходах транзисторов 9 и 10 изменяются с разными температурными

25 коэффициентами. Это приводит к увеличению коллекторного тока транзистора 9 и, следовательно, эмиттерных токов транзисторов 1 и

2. Последнее обстоятельство компенсирует дрейф токов базы этих транзисторов, обус30 ловленный температурной зависимостью ста

45@ 4!

Составитель В. Анисимов

Техред Л. Морозова

Корректор Н. Лебедева

Редактор Б. Федотов

Заказ 636/6 Изд. № 373 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, jK-35, Раушская наб., д. 4, 5

Типография, пр, Сапунова, 2 тистических коэффициентов усиления по току.

При подаче на вход ДУ дифференциального напряжения коллекторные токи транзисторов в одном из плеч уменьшаются, а в другом увеличиваются. Выходное напряжение предварительного каскада снимается с резисторов нагрузки и усиливается выходным каскадом.

Предмет изобретения

Дифференциальный усилитель, содержащий последовательно соединенные входной балансный каскад на транзисторах, включенных по схеме с общим коллектором, предварительный балансный каскад на транзисторах, включенных по схеме с общим эмиттером, и выходной балансный каскад на транзисторах с резистивным делителем в его общей эмиттерной цепи, к средней точке которого подключены базы транзисторов генера5 торов тока, причем коллектор одного из них включен в общую эмиттерную цепь предварительного каскада, а коллектор транзистора другого генератора тока через резистор соединен с эмиттером транзистора одного из

I0 плеч входного каскада, отл ич а ющи йс я тем, что, с целью повышения стабильности режима работы транзисторов, коллектор транзистора второго генератора тока через резистор соединен с эмиттером транзистора

15 другого плеча входного каскада, а эмиттеры транзисторов генераторов тока соединены между собой через резистор.