Логическая дифференцирующая цепочка

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (i i) 459855

Союз Советских

Социалистических республик (61) Зависимое от авт. свидетельства (22) Заявлено 05.05.72 (21) 1781682/26-9 с присоединением заявки № (23) Приоритет

Опубликовано 05.02.75. Бюллетень № 5

Дата опубликования описания 24.03.75 (51) М. Кл. Н 03k 19j00

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.374.3 (088.8) (72) Авторы изобретения

В. И. Дениско и С. Э. Якубайтис (7! ) Заявитель (54) ЛОГИЧЕСКАЯ ДИФФЕРЕНЦИРУЮЩАЯ ЦЕПОЧКА

Изобретение относится к квазиэлектронной

АТС и коммутаторам, а также к устройствам автоматического регулирования.

Известна логическая дифференцир ующая цепочка, содержащая два формирователя, объединенных по управляющему входу через инвертор. Недостатком подобного устройства является большое количество элементов.

Цель изобретения — упрощение схемы достигается тем, что управляющий вход предлагаемой логической дифференцирующей цепочки подключен к первому входу первой схемы «И — HE» и черсз инвертор — к первому входу второй схемы «И — HE», первые входы третьей и четвертой схем «И вЂ” НЕ» соединены соответственно с прямым и инверсным выходами триггера разрешения, а вторые входы этих же схем подключены ко входным клем мам тактовых нмп Ibcon, выходы второй и четвертой схем «И вЂ” HE» соединены соответственно с инверсными входами триггеров разрешения и запрета, выходы первой и третьей схем «И вЂ” НЕ» подключены к пр";— мым входам триггеров разрешения и запрета соответственно, а входы пятой и шестой выходных схем «И вЂ” НЕ» соединены соответственно с прямым и инверсным выходами триггеров разрешения и запрета.

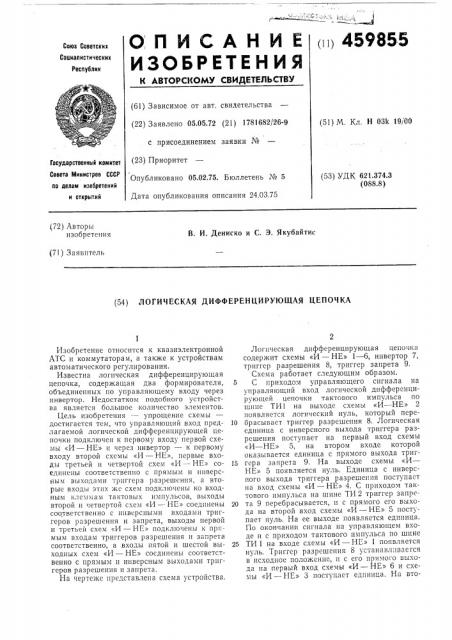

На чертеже представлена схема устройства.

Логическая дифференцирующая цепочка содержит схемы «И — HE» 1 — 6, инвертор 7, триггер разрешения 8, триггер запрета 9.

Схема работает следуюшим образом.

С приходом управляющего сигнала на управляющий вход логической дифференцирующей цепочки тактового импульса по шине ТИ1 на выходе схемы «И — НЕ» 2 появляется логический нуль, который nepeI0 брасывает триггер разрешения 8. Логическая единица с инверсного выхода триггера разрешения поступает на первый вход схемы

«И — HE» 5, на втором входе которой оказывается единица с прямого выхода триг15 гера запрета 9. На выходе схемы «И—

НЕ» 5 появляется нуль. Единица с инверсного выхода триггера разрешения поступает на вход схемы «И — НЕ» 4. С приходом тактового импульса на шине ТИ2 триггер запре20 та 9 перебрасывается, и с прямого его выхода на второй вход схемы «И — НЕ» 5 поступает нуль. На ее выходе появляется единица.

По окончании сигнала на управляющем входе и с приходом тактового импульса по шине

25 ТИ 1 на входе схемы «И — HL» 1 появляется нуль. Триггер разрешения 8 устанавливаегся в исходное положение, и с его прямого выхода на первый вход схемы «И — HE» 6 и схемы «И — НЕ» 3 поступает единица. На вто459855

Упраол

g«gJ

Составитель В. Дениско

Техред Л. Морозова

Корректор Л. Орлова

Редактор Б. Федотов

Заказ 636j16 Изд. № 373 Тираж 902 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д, 4!5

Типография, пр, Сапунова, 2 рой вход схемы «И — HE» 6 поступает единица с инверсного выхода триггера запрета 9. На входе схемы «И — HE»6 появляется нуль. С приходом тактового импульса по шине ТИ 1 на схему «И — НЕ» 3 на ее выходе появляется нуль, триггер запрета перебрасывается. На второй вход схемы «И — НЕ» 6 с инверсного выхода триггера запрета поступает нуль, на выходе схемы «И — HE» 6 появляется единица.

Схема логической дифференцирующей цепочки вновь готова к поступлению сигнала по управляющему входу.

Предмет изобретения

Логическая дифференцирующая цепочка, содержащая шесть схем «И вЂ” НЕ», инвертор, триггер разрешения и триггер запрета, отличающаяся тем, что, с целью упрощения схемы, управляющий вход логической дифференцирующей цепочки подключен к первому входу первой схемы «И — НЕ» и через инвертор — к первому входу второй схе5 мы «И — НЕ», первые входы третьей и четвертой схем «И вЂ” НЕ» соединены соответственно с прямым и инверсным входами триггера разрешения, а вторые входы этих же схем подключены ко входным клеммам тактового

lO питания, выходы второй и четвертой схем

«И — HE» соединены соответственно с инверсными входами триггеров разрешения и запрета, выходы первой и третьей схем «И—

НЕ» подключены к прямым входам триггеров

15 разрешения и запрета соответственно, а входы пятой и шестой выходных схем «И—

НЕ» соединены соответственно с прямым и инверсным выходами триггеров разрешения и запрета.