Цифровой интегратор

Иллюстрации

Показать всеРеферат

p, " "еснеф1 (ii 4605ИОГ1ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 05.02.73 (21) 1880055/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 15.02.75. Бюллетень № 6

Дата опубликования описания 08.04.75 (51) М. Кл. б 06j 3/00

Государственный комитет

Совета Министров СССР (53) УДК 681.34(088.8) по делам изобретений и открытий (72) Авторы изобретения А. Л. Гуревич, Л. А. Русинов, Н, A. Сягаев и В. Н. Соколов (71) Заявитель Ленинградский ордена Трудового Красного Знамени технологический институт имени Ленсовета (54) ЦИФРОВОЙ ИНТЕГРАТОР

Изобретение относится к области автоматики и вычислительной техники, в частности, оно может быть использовано для обработки данных, поступающих с хроматографического анализатора, в которых входной сигнал после соответствующего нормирования во входном блоке преобразуется в код или частоту и интегрируется.

Известны устройства, производящие следящее аналоговое измерение базисного сигнала в моменты отсутствия пика.

Недостатком известных устройств является наличие погрешности от нестабильности аналоговых запоминающих устройств, в частности, использующих конденсаторы, Цель изобретения состоит в повышении точности устройства.

Эта цель достигается тем, что в предлагаемый генератор введены преобразователь кодов, реверсивный счетчик, входы которого соединены с выходами аналого-цифрового преобразователя и через преобразователь кодов— с регистром базисного сигнала, и триггер знака, подключенный к выходам реверсивного счетчика, соединенным с первыми входами дополнительно введенных схем «И», вторые входы которых подключены к выходам триггера знака, выходы дополнительных схем «И» связаны с соответствующими входами регистра базисного сигнала, а выход одной из них подключен ко второму входу схемы «И», связанной со входом счетчика интеграла.

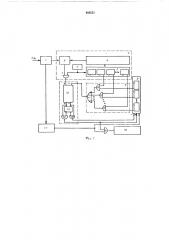

На фиг. 1 приведена структурная схема интегратора; на фиг. 2 — диаграммы, поясняющие его работу.

Сигнал с хроматографа У„поступает на входной блок 1, где усиливается и нормируется, и далее на развертывающий аналогоцифровой преобразователь (АЦП) 2, включающий счетчик 3, преобразователь код †напряжение (ПКН) 4, включенный в цепь обратной связи, генератор 5 тактовых импульсов и схему сравнения 6, управляющую вентилем 7, с выхода которого снижается единичный код.

Для равномерного распределения импульсов кода в интервале преобразования триггеры счетчика 3 управляют разрядными ячейками ПКН 4 дополнительного веса. Код базисного значения U„сигнала хроматографа, запомнен20 ного в регистре 8 базисного сигнала, преобразуется преобразователем кодов 9 в каждом цикле преобразования АЦП 2 в единичный код и вычитается из кода входного сигнала.

Преобразователь кодов 9 состоит из разряд25 ных двухвходовых вентилей 10, соединяемых попарно с единичными выходами соответствующих триггеров счетчика 3 и регистра 8.

Выходы вентилей 10 соединены со схемой

«ИЛИ» 11, на выходе которой и образуется

30 единичный код. Вычитание кодов осуществля460551 ется в реверсивном счетчике 12, входные шины которого соединены с выходами схем 7 и

«ИЛИ» 11. На выходе счетчика установлен триггер знака 13, контролирующий знак числа в счетчике 12. Выходные шины триггера знака связаны со схемами «И» 14 и 15, вторые входы которых соединены с шинами переноса счетчика 12, а выходы — со входами регистра

8 базисного сигнала и входом схемы «И» 16.

Второй вход схемы «И» 16 соединен с блоком управления 17, а выход — со входом счетчика интеграла 18. Слежение за базисным сигналом хроматографа осуществляется при отсутствии полезного сигнала, что определяется блоком управления 17. В это время в регистр 8 базисного сигнала поступают импульсы из счетчика 12. При обнаружении полезного сигнала блок 17 запрещает поступление сигналов в регистр 8 и открывает схему «И» 16, соединенную со входом счетчика интеграла 18.

Коррекция погрешности, вызванной запаздыванием обнаружения пика, осуществляется следующим образом.

Входной сигнал через входной блок 1 подается на один вход схемы сравнения 6 АЦП 2, на второй вход которой подается напряжение обратной связи с ПКН 4. Тактовые импульсы генератора 5 поступают на вход счетчика 3 и опрашивают схему 7. При U,,) U,, схема

7 разрешает поступление импульсов единичного кода U,, на выход преобразователя АЦП 2.

Для равномерного распределения входных импульсов счетчик 3 управляет ячейками

ПКН 4 дополнительного веса (заполняется со старших разрядов) .

Пример импульсной последовательности приведен на фиг. 2. Импульсы с единичных выходов триггеров счетчика 3 опрашивают вентили 10 преобразователя кодов 9, управляемые триггерами регистра 8, так что число опросов за цикл счетчика равно весу разряда кода регистра. Импульсные последовательности входного кода и кода базисного сигнала поступают на реверсивный счетчик 12, соответственно на суммирующий и вычитающий его входы. Знак числа в счетчике контролируется триггером 13, управляемым переносами из счетчика 12. Скорость отработки рассогласования между входным и базисным сигналами зависит от его величины.

При обнаружении пика блок управления 17 запрещает поступление сигналов в регистр 8 и открывает схему «И» 16, Импульсы переноса из счетчика 12, представляющие разность

U„.„— У„будут поступать на счетчик интеграла 18.

Предмет изобретения

20 Цифровой интегратор, содержащий аналогоцифровой преобразователь, блок управления, связанный со входом устройства и входами схемы «И» и регистра базисного сигнала, и счетчик интеграла, отличающийся тем, 25 что, с целью повышения точности устройства, в него введены преобразователь кодов, реверсивный счетчик, входы которого соединены с выходами аналого-цифрового преобразователя и через преобразователь кодов — с регистЗО ром базисного сигнала, и триггер знака, подключенный к выходам реверсивного счетчика, соединенным с первыми входами дополнительно введенных схем «И», вторые входы которых подключены к выходам триггера знака, 35 выходы дополнительных схем «И» связаны с соответствующими входами регистра базисного сигнала, а выход одной из них подключен ко второму входу схемы «И», связанной со входом счетчика интеграла.

460551

Редактор Б. Нанкнна

Заказ 791/17 Изд. № 1126 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Я-35, Раушская наб., д. 4/5

Типография, пр, Сапунова, 2

Вб/А 5

Е7бЬГ 7

Составитель С. Белан

Техред А. Камышникова Корректор Н. Стельмах