Триггер

Иллюстрации

Показать всеРеферат

ОПИСАНИЕИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

- — - п1) 462275

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства— (22) Заявлено 06.12.72 (21) 1853300/26-9 с присоединением заявки №вЂ” (32) Г1риоритет—

Оп бликовано 28.02.75. Бюллетень ¹ 8 (51) М. Кл, Н 03k 3/286 (осударственный номитет

Совета Министров СССР

llQ делам изобретений и открытии (53) УДК 681.327 (088.8) Дата опубликования описания 07.08.75 (72) Автор изобретения

С. В. Ротнов

Московский ордена Трудового Красного Знамени инженерно-физический институт (71) Заявитель (54) ТРИГГЕР

Изобретение относится и арифметическим и управляющим устройствам ЭЦВМ и цифровой автоматики.

Известен триггер, содержащий две логические схемы «И-НЕ», охваченные обратной связью, и две схемы управления.

Целью изобретения является снижение потребляемой мощности и повышение надежности триггера.

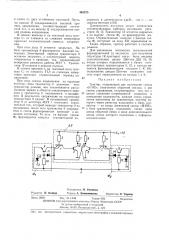

Для этого в предлагаемом триггере каждая схема управления выполнена па транзисторе, эмиттер которого через резистор подключен к базе, коллектор — ко входу логической схемы «И-НЕ», к базе транзистора подключен также анод диода обратной связи и анод дополнительного диода, катод которого образует информационный вход.

На чертеже представлена схема предлагаемого триггера.

Устройство состоит из бистабильпой ячейки (БЯ), образованной перекрестным соединением двух логических схем «И-НЕ» и схем управления Ф и Ф2.

В логических элементах «И-НЕ» многоэмиттерные транзисторы (МЭТ) 1 и 2 и резисторы 3 и 4, подключающие базы МЭТ к источнику питающего напряжения Е, образуют схемы «И». Транзисторы 5 и 6 и резисторы

7 и 8, подключающие коллекторы транзисторов о, b к источнику питающего напряженпя Е, осуществляют инверсию сигналов, подаваемых на входы МЭТ, Перекрестные обратные связи с коллекторов транзисторов 5 и

6 на входы МЭТ 2 и 1-позволяют образовать

БЯ. Коллекторы транзисторов 5 и 6 являются соответственно выходами Q u Q триггера.

Схема управления Ф1 состоит из транзистора 9, коллектор которого соединен с эмиттерным входом МЭТ 1, а эмиттер через резит О стор 10 подключен к базе. Диод Шоттки (ДШ) 11 связывает базу транзистора 9 с выходом триггера Q (коллектор транзистора 6).

Схема управления Фо аналогична Фп строится на транзисторе 12, резисторе 13, диоде

Шоттки 14. Включение Фе в БЯ подобно включению Фь Эмиттеры транзисторов 9 и 12 объединены и образуют тактовый вход С . Использование диодов Шоттки в цепи обратной связи позволяет более надежно запереть транзистор формирователя, не образующего импульса в данном такте.

Работа триггера в счетном режиме протекает следующим образом.

25 В исходном состоянии на вход триггера Ср от стандартного логического элемента ТТЛ

«И-НЕ» со сложным инвертором подан низкий уровень напряжения, соответствующий логическому «О». Транзисторы 9, 12, диоды 11, ЗО 14 закрыты, а бистабильная ячейка находится

462275

БЯ

Составитель И. Разинова

Техред А. Камышиикова

Редактор Н. Коляда

Корректор О. Тюрина

Заказ 3065 Изд Х> 1248 Тираж 902 Подписное

ЦИИИПИ Государствепного комитета Совета Министров СССР по делам изобретений и открытий;

Москва, Ж-35, Раушская наб., д. 4/5

Обл. тип, Костромского управления издательств, полиграфии и книжной торговли в одном нз двух устойчивых состояний. Пусть на выходе Q поддер>кивается высокий уровень напря>кения, соответствующий логической «1», а на выходе Q поддерживается низкий уровень напря>кения.

В момент времени fo Ha тактовый вход триггера Сп от элемента со сложным ннвертором приходит положительный перепад напряжения.

При этом диод 11 остается закрытым. На базе транзистора 9 фиксируется высокий потенциал. Эмиттерный переход транзистора 9 остается закрытым, а коллекторный переход открывается и проводит ток, определяемый инверсным режимом работы МЭТ 1. Транзистор 12 остается в режиме отсечки.

В момент времени t на тактовый вход триггера С от элемента ТТЛ со сложным инвертором приходит отрицательный перепад напряжения.

При этом скачок напряжения на переходе эмиттер — база транзистор 9 включает этот транзистор раньше, чем заканчивается рассасывание заряда в области коллекторного перехода и транзистор 9 оказывается в насыщении. В результате напря>кение на коллекторе транзистора 9 падает. В насыщенный транзистор 9 от эмиттера МЭТ 1 поступает значительный ток, который выводит транзистор 9 из насыщения, после чего транзистор 9 закрывается и схема формирователя приходит в исходное состояние. То есть на выходе схемы

Ф1 формируется импульс отрицательной полярности и длительности т)2l :, где и — задержка вентиля в БЯ.

Длительность импульса может изменяться соответствующим выбором номиналов регистров 10, 13. Транзистор 12 остается закрытым и на выходе схемы Ф не формируется импульс. Отрицательный импульс с выхода схемы Ф1 поступает на вход БЯ; переключая ее.

Таким образом, триггер работает в счетном

10 режиме

Для увеличения логических возмо>кностей формирователей (в частности для получения структуры 1К-триггера) могут быть введены дополнительные диоды Шоттки ДШ 15, 16, аноды которых подключаются к базам соответствующих транзисторов 9, 12, а катоды являются функциональными входами 1, К. Использование диодов Шоттки позволяет снизить порог переключения по входам 1 и К.

Предмет изобретения

Триггер, содержащий две логические схемы

«И-НЕ», охваченные обратной связью, н две схемы управления, отличаюшиася тем, что с

25 целью снижения потребляемой мощности и повышения надежности, каждая схема управления выполнена на транзисторе, эмиттер которого через резистор подключен к базе, коллектор — ко входу логической схемы «И-НЕ», к базе транзистора подключен также анод диода обратной связи и анод дополнительного диода, катод которого подключен к информационной шине.