Устройство для обработки и контроля данных

Иллюстрации

Показать всеРеферат

11дТт; юзнАуу

Ф:, ч -т ИИнблидтека щв

<п1 463975

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соаатсеи

Фаиианиотичеаиих

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 30.11.73 (21) 1973447/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 15.03.75. Бюллетень № 10

Дата опубликования описания 16.06.75 (51) М. Кл. G 061 11/00

Государственный комитет

Совета Министров СССР по дедам изобретений и открытий (53) УДК 681.17(088.8) (72) Авторы изобретения Б. В. Городецкий, А. И. Плющев, А. П. Самойленко и В. И. Финаев

Таганрогский радиотехнический институт (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ И КОНТРОЛЯ

ДАННЫХ

Изобретение относится к области вычислительной техники и телемеханики, а также к области контроля функционирования устройства для обработки данных.

Известно устройство для обработки и контроля данных, содержащее процессоры, первые входы которых соответственно соединены через первые и вторые ключи с соответствующими шинами ввода информации. Выходы процессоров через третьи ключи соответственно соединены со входами регистров сдвига, через четвертые ключи соответственно — с первыми входами компараторов, а также через пятые ключи соответственно — со вторыми входами ком параторов. Выходы регистров сдвига подключены через шестые ключи ко вторым входам соответствующих процессоров, а также через седьмые ключи — ко вторым входам соответственно предыдущих процессоров. Входы первых, третьих, пятых, шестых и седьмых ключей нечетных процессоров и входы вторых и четвертых ключей четных процессоров подключены к первой управляющей шине. Входы вторых, пятых, шестых, третьих и седьмых ключей четных процессоров и входы вторых и четвертых ключей нечетных процессоров подключены ко второй управляющей шине. Известное устройство содержит также индикатор и триггеры.

К недостатку известного устройства следует отнести излишние аппаратурные затраты при реализации контроля функционирования устройства для обработки информации.

Цель предлагаемого изобретения заключа5 ется в упрощении устройства.

Цель достигается тем, что в устройство введены элементы «ИЛИ», а триггеры выполнены с тремя устройчивыми состояниями. Выходы компараторов соединены с первыми вхо10 дами соответствующих схем элементов

«ИЛИ», а также соответственно со вторыми входами последующих элементов «ИЛИ», выходы которых подключены к единичным входам соответствующих триггеров, входы уста15 нонки «О» которых соединены с тактовой шиной. Двоичные выходы триггеров соединены с соответствующими входами индикатора.

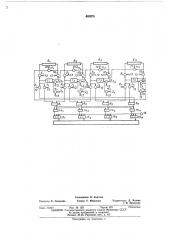

На чертеже представлена схема устройства.

20 Предлагаемое устройство содержит процессоры 1> — 1, ключи 2> — 2, входы 31 — 3 ввода информации, ключи 4> — 4„и 51 — 5„„, регистры 61 — 6„.сдвига, ключи 71 — 7, компараторы 8> — 8„, ключи 9 — 9, 101 — 10„и 11—

25 11„, управляющие шины 12 и 13, элементы

«ИЛИ» 141 — 14„, триггеры 15 — 15„, тактовую шину 16 и индикатор 17.

Устройство работает следующим образом.

Управление работой устройством для обра30 ботки данных осуществляется подачей управ463975

15 ляющих импульсов 51 и t> соответственно, на шины 12 и 1д.

J5o время действия первого управляющего импульса 1 входные данные, соответственно, подаются через ключи 2ь 2з,... 2 1 на входы только нечетных процессоров первой группы, а также — в определенные четные процессоры второй группы посредством ключеи ч, 44,..., 4 „, т. е. входные данные, предназначенные для процессора ь подаются также и на вход процессора „, данные, поданные на вход процессора, подаются также и на вход процессора

14+1 (c= 1, 5,..., и — 1) и T. д.

0 течение действия второго управляющего импульса t> входные данные подаются соответственно через ключи 2>, 24,..., 2п на входы только четных процессоров 1 второй группы, а также — в соответствующие нечетные процессоры посредством ключей 4ь 4,..., 4„ь

Регистры о1 — b состоят из подрегистров, количество которых определяется фазностью регистров, например восемь подрегистров.

К,оммутация подрегистров нечетных регистров оь bq,..., Ь со входами и выходами соответствующих процессоров lь 1>,..., 1„1 производится последовательностью импульсов равной длительности (tqi8), общая длительность которой равна 4. Каждыи подрегистр на соответствующем такте (i, 8, 0,..., 15) осуществляет вместе с соответствующим процессором обраоотку информации и контроль функционирования его на каждом из тактовуправляющего импульса t>. Выходные данные соседних процессоров попарно (1 и 2, 2 и 8 ..., и и l) подаются на входы соответствующих компараторов 8> — 8„, которые выдают единичный сигнал в случае, когда результаты, полученные на выходах этих процессоров, обраоатывающих одну и ту же информацию, не совпадают. Компараторы реализуют логическую функцию «1 1сключающее ИЛИ». Коммутация подрегистров четных регистров 6, 64..... 6 со входами и выходами соответствующих процессоров 1, 14,..., 1 производится последовательностью импульсов равной длительности (4/8), общая длительность которой составляет t>. Каждый подрегистр на соответствующем такте (2, 4, ...,16) осуществляет как ооработку информации, так и контроль функционирования соответствующего четного процессора.

При отказе (ошибке) одного и более процессоров, например .процессора 1, появляются на выходах соответствующих пар компараторов единичные сигналы, например на

4 паре компараторов 8> и 8 за время действия импульсов 4 и t>. Соответствующие троичные триггеры 151 — 15, находящиеся в исходном состоянии 100, фиксируют единичные сигналы, например триггеры 15 и 15> переходят в состояние 0i0. Но благодаря наличию функциональной связи между выходами компараторов bi — 8 и входами элементов «ИЛИ»

i4> — 14„, триггеры одноименных цепей с отказавшими процессорами фиксируют двоинои сигнал, переходя в состояние iUi, например триггер 15 фиксирует сигнал от компараторов 8i и Ь, Индикатор 1 /, получив единичные сигналы от двоичных выходов триггеров 15i— о, опознает неисправный процессор.

Предмет изобретения

Устройство для обработки и контроля данных, содержащее процессоры, первые входы которых соответственно соединены. через первые и вторые ключи с соответствующими шинами ввода информации, выходы процессоров через третьи ключи соответственно соединены со входами регистров сдвига, через четвертые ключи соответственно — с первыми входами компараторов, а также через пятые ключи соответственно — со вторыми входами компараторов, выходы регистров сдвига подключены через шестые ключи ко вторым входам соответствующих процессоров, а также через седьмые ключи — ко вторым входам соответственно предыдущих процессоров, входы первых, третьих, пятых, шестых и седьмых ключей нечетных процессоров и входы вторых и четвертых ключей четных процессоров подключены к первой управляющей шине, входы вторых, пятых, шестых, третьих и седьмых ключеи четных процессоров и входы вторых и четвертых ключей нечетных процессоров подключены ко второи управляющей шине, а также индикатор и триггеры, о т л и ч аю щ е е с я тем, что, с целью упрощения устройства, в него введены элементы «ИЛИ», а триггеры выполнены с тремя устойчивыми состояниями, причем выходы компараторов соединены с первыми входами соответствующих элементов «ИЛИ», а также соответственно со вторыми входами последующих элементов

«ИЛИ», выходы которых подключены к единичным входам соответствующих триггеров, входы установки «0» которых соединены с тактовой шиной, двоичные выходы триггеров соединены с соответствующими входами индикатор а.

463975

Составитель И. Фирсова

Техред Т. Миронова

Корректоры: Л. Котова и В. Брыксина

Редактор Е. Семанова

Типография, пр. Сапунова, 2

Заказ 1340/7 Изд. № 1251 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5