Многоканальный дискретный коррелятор

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (1п 463978

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Oowe Соеетскик

Вецианнстичеоких

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 15.02.72 (21) 1747756/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 15.03.75. Бюллетень № 10

Дата опубликования описания 16.06.75 (51) М. Кл. б 061 15/34

Государственный комитет Совета Министров СССР ло дедам изобретений и открытий (53) УДК 681.519(088.8) (72) Авторы изобретения

И. Б. Борисов, М. А. Раков, В. М. Тузов и Б. М. Тузов

Физико-механический институт АН Украинской ССР (71) Заявитель (54) МНОГОКАНАЛЪНЫЙ ДИСКРЕТНЫЙ КОРРЕЛЯТОР

Предлагаемое изобретение относится к области вычислительной техники и может быть применено в устройствах цифровой обработки сигналов.

Известен многоканальный дискретный коррелятор, содержащий дискретизатор, генератор импульсов, ряд каналов, включающих линию задержки, дискретные схемы умножения и счетчики импульсов, и устройство, коммутирующее выходы каналов, Однако известный многоканальный дискретный коррелятор имеет относительно узкую полосу частот Л/ анализируемого сигнала.

С целью расширения полосы анализируемого сигнала предлагаемый многоканальный дискретный коррелятор содержит блок стробирования, первый и второй входы которого подключены соответственно к выходам генератора импульсов и дискретизатора, первый и второй выходы блока стробирования соединены соответственно со вторыми входами элементов задержки и вторыми входами схем умножения соответствующего канала, а третьи входы первых схем умножения (n — 1) ка. палов подключены к соответствующему этому каналу третьему выходу блока стробирования.

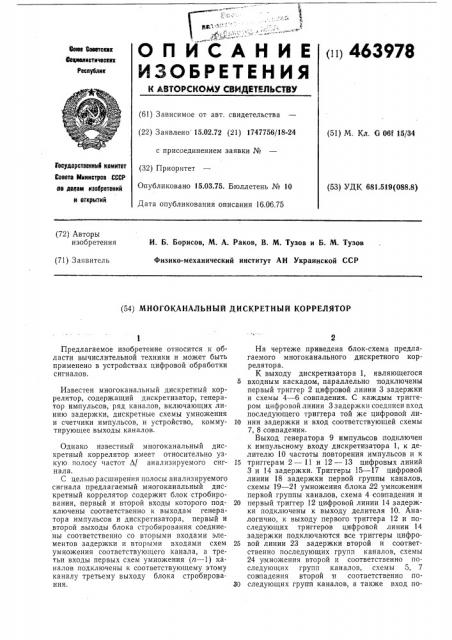

На чертеже приведена блок-схема предлагаемого многоканального дискретного коррелятора.

К выходу дискретизатора 1, являющегося

5 входным каскадом, параллельно подключены первый триггер 2 цифровой линии 3 задержки и схемы 4 — 6 совпадения. С каждым триггером цифровой линии 3 задержки соединен вход последующего триггера той же цифровой ли10 нии задержки и вход соответствующей схемы

7, 8 совпадения.

Выход генератора 9 импульсов подключен к импульсному входу дискретизатора 1, к делителю 10 частоты повторения импульсов и к

15 триггерам 2 — 11 и 12 — 13 цифровых линий

3 и 14 задержки. Триггеры 15 — 17 цифровой линии 18 задержки первой группы каналов, схемы 19 — 21 умножения блока 22 умножения первой группы каналов, схема 4 совпадения и

20 первый триггер 12 цифровой линии 14 задержки подключены к выходу делителя 10. Аналогично, к выходу первого триггера 12 и последующих триггеров цифровой линии 14 задержки подключаются все триггеры цифро25 вой линии 23 задержки второй и соответственно последующих групп каналов, схемы

24 умножения второй и соответственно последующих групп каналов, схемы 5, 7 совпадения второй и соответственно по30 следующих групп каналов, а также вход по463978

50 корреляционной

3 следующего триггера цифровой линии 14 задержки.

Выход схемы 4 совпадения подключается к первому триггеру 15 цифровой линии 18 задержки и ко всем схемам 19 — 21 блока 22 умножения первой группы каналов. Для второй и последующей групп каналов выход схемы 7 совпадения и соответственно последующих схем совпадения, включая схему 8 совпадения для последней группы 25 каналов, подключен к первому триггеру цифровой линии

23 задержки второй и соответственно последующих групп каналов, а также к схеме умножения первого канала второй и соответственно последующих групп каналов. Выходы схемы 5 совпадения второй группы и последующих схем совпадения, включая схему 6 совпадения последней группы 25,каналов, подключены к входам всех схем умножения соответствующей группы каналов. Делитель 10 частоты, цифровые линии 3 и 14 задержки и схемы 4 — 8 совпадения образуют блок 26 стробирования.

Внутри каждой группы каналов выход каждого триггера 15 — 17 цифровой линии 18 задержки подключается к-схеме 19 — 21 умножения соответствующего канала. Выходы блоков 22, 24 умножения подключаются к соответствующим блокам 27 и 28 счетчиков

29 — 31 импульсов, выходы которых коммутируются коммутатором 32.

Работа предлагаемого многоканального дискретного коррелятора происходит следующим образом.

Сигнал, поступающий на вход коррелятора, управляет работой дискретизатора 1. При положительном значении входного сигнала на выход дискретизатора проходят тактовые импульсы .генератора 9, а при отрицательном значении тактовые импульсы не проходят. На выходе делителя 10 частоты формируются импульсы, частота следования которых в п раз меньше частоты следования тактовых импульсов. С выхода дискретизатора 1 сигнал, поступающий на схему 4 совпадения, стробируется импульсами с выхода делителя 10, так что на входе первой группы каналов, содержащей линию 18 задержки, блок 22 схем умножения и блок 27 счетчиков, частота импульсной последовательности в п раз меньше, чем частота импульсного сигнала на выходе дискретизатора 1. Сигнал, идущий с выхода схемы 4 совпадения, далее обрабатывается обычным образом, т. е. для построения корреляционной функции он задерживается, перемножается со своей задержанной копией и поступает на входы счетчиков 29 — 31.

Импульсы генератора 9 тактируют две цифровые линии 3 и 14 задержки, так что задержка каждого триггера 2... 11 и 12....13 равна периоду Лт следования тактовых импульсов. Сигнал с выхода дискретизатора 1, задержанный на время Лт, триггером 2 стробируется в схеме 7 совпадения импульсами делителя частоты, задержанным на то же время

Лт триггером 12. Полученная последовательность импульсов поступает на схему умножения первого канала, входящую в состав блока 24 умножения, второй группы каналов и на цифровую линию 23 задержки второй группы канало в. Кроме того, импульсы диокретизатора 1 без задержки поступают на схему 5 совпадения, где стробируются той же последовательностью задержанных импульсов делителя частоты, а с выхода схемы 5 совпадения поступают на схемы умножения блока 24 второй группы каналов.

Так как стробирование в обеих схемах 5 и

7 совпадения осуществляется одной и той же последовательностью задержанных импульсов делителя частоты, которая, кроме того, тактирует цифровую линию 23 задержки второй группы каналов, то импульсы, поступающие на три входа схем умножения блока 24 являются синхронизированными.

Таким образом, первый канал второй группы каналов определяет значение корреляционной функции К(Лт), второй канал—

К(аЛт+Лт), третий канал — К(2аЬт+Лт) и так далее. Аналогично работают остальные группы каналов, включая последнюю группу каналов 25, с той разницей, что на схемы совпадения j-ой группы каналов сигнал с выхода дискретизатора 1 поступает задержанным на (i — 1) Ьт и стробируется импульсами делителя 10 частоты, также задержанными на (— 1) Лт. Соответственно первый канал

/-ой группы каналов определяет значение корреляционной функции К(1 — 1) Ьт, второй канал j-ой группы каналов — К(пЛт+ (j— — 1) Лт), третий канал — К(2а Лт+ (j — 1) Лт) и так далее, Так как рассматриваемый коррелятор содержит п групп каналов, каждая из которых

М включает т= — каналов, то в результате п определяются все N точек функции.

Тактирование каждой группы каналов импульсами с частотой в п раз меньшей частоты генератора импульсов позволяет в и раз увеличить полосу частот анализируемого сиг. нала.

Предмет изобретения

Многоканальный дискретный коррелятор, каждый из п каналов которого содержит m последовательно соединенных элементов задержки, вторые входы которых, подключены к первым входам соответствующих схем умножения, вторые входы которых соединены со входом первого элемента задержки, третьи входы первой схемы умножения первого канала и (т — 1) схем умножения остальных (п — 1) каналов подключены к выходам соответствующих элементов задержки, выходы схем умножения связаны со входами соответствующих счетчиков импульсов, выходь.

463978 2б

Составитель В. Тузов

Техред Т. Миронова

Корректоры: Л. Денисова и 3. Тарасова

Редактор Т. Янова

Заказ 1340/9 Изд. № 1251 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 которых подключены ко входам выходного коммутатора, а также генератор импульсов, выход которого соединен со входом дискретизатора, о т. л и ч а ю шийся тем, что, с целью расширения полосы частот анализируемого сигнала, он содержит блок стробирования, первый и второй входы которого подключены соответственно к выходам генератора импульсов и дискретизатора, первый и второй выходы блока строоирования соединены соответственно со вторыми входами элементов задержки и вторыми входами схем умноже5 ния соответствующего канала, а третьи входы первых схем умножения (n — 1) каналов подключены к соответствующему этому каналу третьему выходу блока стробирования.