Одноразрядный сумматор

Иллюстрации

Показать всеРеферат

г =-о!

1; 1, -э

ОПИСАНИЕ

ИЗОЬГЕтИНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ р> 463990

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 17.11.72 (21) 1847890/18-24 с присоединением заявки № (51) М. Кл. G 06j 3/00 (23) Приоритет

Государственный комитет

Совета Министров СССР

Опубликовано 15.03.75. Бюллетень № 10

Дата опубликования описания 23.07.75 (53) УДК 681.34(088.8) по делам изобретений н открытий (72) Авторы изобретения

Г. Е. Пухов, В. Ф. Евдокимов, А. С. Огир и Ю. Т. Кизим

Институт электродинамики AH Украинской ССР (71) Заявитель (54) ОД Н О РАЗ РЯДН Ъ| Й СУММАТОР

U эоны — 15нд

nf — 1 ед.

2 т . эоны—

Изобретение относится к области гибридной вычислительной техники.

Известно устройство для суммирования сигналов одной полярности в двоичной системе счисления, содержащее линейку резисторов, первые зажимы которых соединены со входами сумматора, и и входных резисторов.

К недостаткам известного устройства относится возможность суммирования сигналов только одного знака, ограничение количества входов за счет того, что алгебраическое суммирование входных сигналов осуществляется посредством пассивных цепей, а также за счет того, что нулевому значению суммы не соответствует нуль напряжения на выходе схемы.

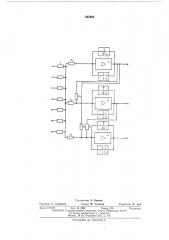

Предложенный сумматор отличается тем, что с целью повышения точности содержит резисторы переноса и и операционных усилителей, в цепи обратной связи каждого из которых включены блок зоны нечувствительности и блок ограничения. Входы операционных усилителей через соответствующие входные резисторы соединены с общей точкой линейки резисторов и через соответствующие резисторы переноса — с выходами последующих операционных усилителей.

Структурная схема одноразрядного сумматора приведена на чертеже, Сумматор содержит линейку резисторов 1, и операционных усилителй 2> — 2, в цепи обратной связи каждого из которых включены блоки ограничения 31 — З„и блоки зоны нечувствительности 4> — 4 . Ко входу каждого усилителя 2 — 2„подключены входные резисторы 5> — 5 и резисторы переноса 61 — 6 .

Резисторы переноса 61 — 6„предназначены для передачи сигнала с выходов операционных усилителей 21 — 2 постоянного тока старших разрядов на вход операционных,усилителей младших разрядов с определенным ко2ш эффициентом передачи К вЂ” . Зоны нечув2

15 ствительности построены следующим образом (от младшего к старшему):

Предложенный сумматор работает следую25 щим образом.

Информация поступает на вход устройства в двоичной системе счисления в знаковом коде 1; 0; — 1, т. е. каждый разряд имеет свой знак. Устройство для случая двоичной систезо мы счисления работает согласно табл. 1.

463990

Таблица 1

Выход

Выход

Выход

Вход (количество единиц) усилителя

2„ усилителя

2л усилителя

2, 3m — !

Таблица 2

Выход

Выход

Выход

Вход усилителя

2> усилителя

2, усилителя

2д

30

+13 — 13 — 1

+1 — 1

+1

+1

+2 3 4 5 6 7

+1 — 1

+2 — 2

+3 — 3

+4

+5 — 5 !

0 !

0 — 1

+1

+1 — 1

0 — 1

+1

+1 — 1

0 1

0 !

0 — 1

+1 — 1

+1 — 1

+1

+1 — 1

0

0 1 !

0

0

0

0 — 1

4

При добавлении еще одного операционного усилдтелр и однрй линейки резисторов 1 количество входов сумматора увеличивается до (2а+1 1)

Для случая работы устройства в троичной системе счисления коэффициент передачи резисторов переноса 61 — 6„ равен К вЂ” 3, а напряжение на зонах нечувствительности

Я1-1 !

0 Уц,кц — — —. и количество резисторов в линей) ке резисторов 1 равно где и — количество двоичных разрядов, необходимых для записи максимальной суммы слагаемых.

20 Устройство для случая троичной системы счисления работает согласно табл, 2 (например, для 13-входного сумматора).

Этот принцип работы справедлив и для одноразрядного сумматора на и входов.

Предмет изобретения

Одноразрядный сумматор, содержащий линейку резисторов, первые зажимы которых соединены со входами сумматора, и и входных резисторов, отличающийся тем, что, с целью пОвыщения точности, он содержит резисторы переносд и и операционных усилителей, в цепи обратной связи каждого из которых включены блок зоны нечувствительности и блок ограничения; входы операционных усилителей через соответствующие входные резисторы соединены с общей точкой линейки резисторов и через соответствующие резисторы переноса — c выходами последующих операционных усилителей.

463990

Составитель А. Наумов

Техред М, Семенов

Корректор Н. Аук

Редактор E. Семанова

Типография, пр. Сапунова, 2

Заказ 1719/17 Изд. Хе 1206 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5