Логическое запоминающее устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е ""464О 7

Союз Советских

Социалистических

Республик

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к BBT. свид-ву-(22) Заявлено 02.10.72 (21) 1833988/18-24 (51) М. Кл. б 11с 15 00 с присоедин IIIIpvl заявки X

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (32) ПриоритетовЂ

01 блнковапо 15.03.75. Бюл IcTc!Ib . хе 10 (53) УДК 681.327.6 (088.8) Дата опубликования описания 02 09.75. (72) Авторы изобретения

В. М. Гриць и А. Н. Пресняков

Особое конструкторское бюро вычислительной техники рязанского радиотехнического института (71) Заявитель (54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к области запоминающих устройств.

Известно логическое запоминающее устройство, содержащее накопитель, входы которого подключены к формирователям адресных и разрядных токов, а выходы — ко входам усилителей воспроизведения, выходы которых соединены с информационными входами схем

«И» первой группы, вторую группу схем «И», схемы «НЕ», регистр числа, подключенный ко входам схем управления, выходы которых соединены со входами формирователей разрядных токов.

11едостатком известного устройства является невысокое быстродействие.

Описываемое устройство отличается от известного тем, что оно содержит дополнительный регистр, входы которого подключены к соответствующим выходам схем «И» первой и второй групп, информационные входы схем

«И» второй группы соединены с выходами схем «НЕ», входы которых соединены с выходами усилителей воспроиз|ведения, в результате значительно повышается быстродействие устройства.

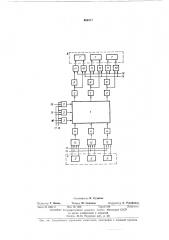

На чертеже изображена блок-схема предлагаемого логического запоминающего устройства, например, типа 2Д и ЗД, выполненного на сердечниках, Устройство содержит накопитель 1, усилители воспроизведения 2, формирователи адресных токов 3, формирователи разрядных токов 4, триггеры 5 регистра числа 6, триггеры 7 дополнительного регистра 8, схемы «НЕ» 9

II две группы схем «И» 10 и 11. Формирователи 4 соедtl!IP!lbl со схемамп 12 управления, на которые поступают сигналы с обоих выходов триггеров 5 регистра числа 6 и синх1юнизнрлощие сигналы с управляющих шин 13 и 14.

1о Выходы усилителей воспроизведения 2 соединены непосредственно с информационнымп входами схем «И» 10 первой группы и через схемы «НЕ» 9 с информационными входамп схем «И» 11 второй гр .ппы, Выходы схем «И»

15 10 и 11 соединены со входами дополнительного регистра 8, а управляющие входы — с управляющими шинами 15 и 16 соответственно.

Входы формирователей 3 подключены к управляющим шинам 17, 18 и 19.

20 Устройство работает следующим образом.

В регистр числа 6 записывается операнд Л, а в -й ячейке памяти накопителя 1 хранится операнд Y. Для выполнения операции «сумма

IIo модулю два» в первом такте по сигналу на шине 17 и адресному сигналу на шине 19 включаются соответствующие формирователии 3, вырабатывающие ток считывания.

Одновременно по сигналу на шине 13 включаются формирователи 4, которые вырабатывают токи запретя считывания в тех разрядах, О

464017

35

50 где в регистре числа 6 хранится «ггуль». При такой комбинации адресного и разрядных сигналов в ячейке памяти формируется результат логической операции «Запрет по Х», а на выходах усилителей воспроизведения 2 — результат «конъюнкции».

В тех разрядах, где выходной сигнал усилителя воспроизведения 2 соответст|вует логическому «нулю» путем инвертирования сигнала с выхода усилителя воспроизведения 2 формируется результат «операции Шеффера», которая является дизъюнкцией «суммы по модулю два»:i «операции Пирса». Выходные сигналы со схем «НЕ» 9 поступают на информационные входы схемы «И» 11, на другие входы которых подается оинхросигнал с шины 16. С выходов схем «И» 11 сигналы поступают на входы «установки нуля» триггеров 7 регистра 8. Во втором такте формирователь 3 по сигналу на шине 18 формирует ток записи, а формирователь 4 по сигналу на ши ге

14 — ток запрета записи «единицы» в тех ра-грядах, где в регистре числа 6 хранится «единица».

Такая комоинация адресных и разрядных токов гперемагнггчггвает запоминающие элементы в тех разрядах ячейки памяти, где хранился

«нуль», кото рый соответствует обратному коду информации, хранимой B запо мггнающей ячейке, т. е. отрицанию «за прета по Х» или

«ггмпликагцнгг от У к Х», и где отсутствует ток запрета записи. В результате на выходах усилителей воспроизведения 2 возникнет код, являющийся результато м поразрядной логиче ской «операции Пирса» двух слов: хранимого до начала операции в ячейке памяти и поступившего на входы триггеров 5 регистра числа

6 перед началом вьгполнения операции. Этот код с выходов усилителей воспроизведения 2 поступает на один из входов схем «И» 10, на другие входы которых поступает сигнал с шины 15. С вьгходов схем «И» 1О сигналы Iioдаются на входы «óñòàtíoâêè нуля» триггеров

7 регистра 8.

В результате такой .коррекцгггг, гпро веденной во втором такте, в регистре 8 образуется «сумма по мод улю два» дв ух слов.

Для выполнения операции «;,oãii÷åoêàÿ равнозначность» выбирается необходимая ячейка и подается синхросигкал по шине 17, который управляет формированием адресното тока считывания, а сигналом на шине 13 включаются формирователи 4, которые вырабатывают токи запрета считывания в тех разрядах, где в

4 регистре 6 хранится «единица». Прп такой комбинации токов в запоминающей ячейке образуется результат «конъюнкции» двух слов, расположенных в регистре 6» одной пз ячеек накопителя 1.

В результате инверсии выходных сигналов усилителей воспроизведеггия 2, соответствующих операции «запрета по Х», на информационные входы схем «И» 11 поступает код, являющийся результатом операции «имнликация от Y к Х», представляющей собой дизьгонкциго «логической равнозначности» и «запрета по У» исходных слов.

На управляющие входы схем «И» 11, объединенные между собой, подается ciiiixpocIII пал с шины 16, разрешающий посту пение сигналов с выходов схем «И» 11 на входы «установки единицы» триггеров 7 регистра хранения результата 8. Во втором такте выбранный формирователь 3 при наличии сигнала на шине 18 выдает импульс тока записи, а формирователи 4 — импульс тока запрета записи в тех разрядах, где в регистре 6 хранится

«нуль», если есть синхросигнал на шине 14.

В результате такого воздействия гна запоминающие элементы на входы схем «И» 1О поступает код, являющийся результатом операции

«запрет по У». При наличии синхросигнала па шине 15 этот код выдается на «нулевые» установочные входы триггеров 7, образуя в регистре 8 результат поразрядной операции «логическая равнозначность».

Предмет изобретения

Логическое запоминающее устройство, содержащее накопитель, входы которого подключены к формирователям адресных и разрядных токов, а выходы — ко входам усилителей воспроизведения, выходы которых соединены с информационными входами схем

«И» первой группы, вторую группу схем «И», схемы «НЕ», регистр числа, подключенный ко входам схем управления, выходы которых соединены со входами формирователей разрядных токов, отличающееся тем, что, с целью увеличения быстродействия, оно содержит дополнительный регистр, входы которого подключейы к соответствующим выходам схем

«И» первой и второй групп, иггформацио нные входы схем «И» второй группы соединены с выходами схем «НЕ», входы которых соединены с выходами усилителей воспроизведения.

464017

19

Составитель В, Рудаков

Техред М. Семенов Корректор Е. Рогайлнна

Редактор Т. Янова

Обл. тиг.. Костромского управления издательств, полиграфии и книжной торговли

Заказ № 3066/11 Изд. № 1240 Тираж 648 Подписное

ЦН11ИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, К-35, Раушская наб., д. 4/5