Устройство для вычисления обратного гиперболического тангенса

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

ОП ИСАЙИ Е

ИЗОБРЕТЕН ИЯ

"ц 465630

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (б1) Дополнительное к авт. свид-ву— (22) Заявлено 03.07.73 (21) 1941193/18-24 с присоединением заявки №вЂ” (32) Приоритет—

Опубликовано 30.03.75 Бюллетень № 12

Дата опубликования описания 21.11.75 (51) М.Кл. 6 06f 7/38

Государственный комитет

Совета Министров СССР па делам изооретений и аткрытий (53) УДК 681.325. .5 (088.8) (72) Авторы

:изобретения

А. Л. Рейхенберг и Р. Я. Шевченко (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ОБРАТНОГО

ГИПЕРБОЛИЧЕСКОГО ТАНГЕНСА

Изобретение относится к области цифровой вычислительной техники и может найти применение при аппаратном вычислении элементарных функций, в частности, в специализированных двоичных цифровых вычислительных машинах с фиксированной запятой.

Известно устройство для вычисления обратного гиперболического таигеиса, содержащее три накопительных сдвигающих регистра, три сумматора-вычитателя, блок псевдочастного и блок управления. Выходы младших триггеров первого, второго и третьего накопительных сдвигающих регистров соединены соответственно с первыми входами первого, второго и третьего сумматоров-вычитателей, а выходы сумматоров-вычитателей — со счетными входами старших триггеров соответствующих накопительных сдвигающих регистров. Выход старшего триггера первого накопительного сдвигающего регистра связан с входом блока псевдочастного, а выход последпего — с входами управления всех сумматоров-вычитателей. Первые три выхода блока управления подключены к сдвигающим входам соответствующих накопительных сдвигающих регистров.

Цель изобретения — повышение быстродействия и упрощение устройства.

Это достигается тем, что в устройство введены два сдвигающих регистра, блок памяти и блок сравнения. При этом информационные входы блока сравнения связаны с соответствующими выходами первого накопительного сдвигающего регистра, а его выход — с входом блока управления. Четвертый и пятый выходы блока управления подключены соответственно к сдвигающим входам первого и второго сдвигающих регистров, ииформаииоиные входы этих регистров — к одноименным информационным выходам соответственно первого и второго накопительных сдвигающих регистров, а выходы младших триггеров — к вторым входам соответственно второго и первого сумматоров-вычитателей. Шестой выход блока управления соединен с входом блока памяти, выход которого соединен с вторым входом третьего сумматора-вычитателя.

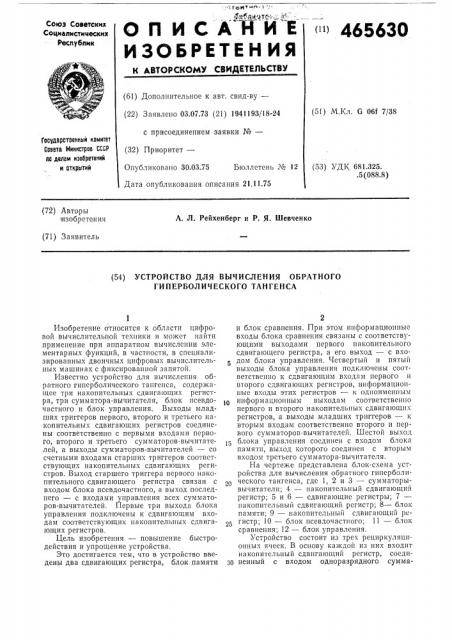

На чертеже представлена блок-схема устройства для вычисления обратного гиперболического тангенса, где 1, 2 и 3 — сумматорывычитатели; 4 — накопительный сдвигающий регистр; 5 и б — сдвигающие регистры; 7— накопительный сдвигающий регистр; 8 — блок памяти; 9 — накопительный сдвигающий регистр; 10 — блок псевдочастного; 11 — блок сравнения; 12 — блок управления.

Устройство состоит из трех рециркуляционных ячеек. В основу каждой из них входит накопительный сдвигающий регистр, соедини ненный с входом одноразрядного сумма465630 тора-вычитателя, выход которого связан с входом этого регистра. Выходы накопительного сдвигающего регистра соединены с информационными входами сдвигающего регистра, а выход сдвигающего регистра— с управляемым входом сумматора-вычитателя другой ячейки. Выход сдвигающего регистра второй ячейки подключен к управляемому входу сумматора-вычитателя первой ячейки.

На управляющий вход сумматора-вычитателя третьей ячейки подан выход блока памяти.

Память, которая введена в устройство, является односторонней. Выход старшего триггера накопительного сдвигающего регистра 4 псевдоделителя соединен с блоком 10 псевдочастного, остальные разряды этого регистра поданы на блок 11 сравнения. Выход блока 11 соединен с блоком 12 управления.

Выходы блока 12 управления, по которым поступают серии сдвигающих тактовых импульсов, соединены со сдвйгающими входами регистров и выборкой памяти, выход блока 10 — с входами управления сумматороввычитателей.

В начальном состоянии в регистре 4 находится аргумент У, в регистре 7 — единица, которая представляется: всеми значащими разрядами справа от двоичной запятой, в накопительном сдвигающем регистре 9 — нулевое значение.

Получение обратного гипероолического тангенса основано на следующих соотношениях:

Уо = У, У;,!= У,.— g Х, 2-/, У, - О, хо = 1, х, = х — !/ у 2 /, х „аап а /г " 1 г/2 л chtt

/о = l, //1! = / + !/ .агй 2 — /,г„- - аtrhg, и

k „= П (l — 2--2 )и

j=-

1, 2; 3, 4, 4, ..., 3/г + 1, 3/г + 1, ..., n.

Указанные разностные рекуррентные соотношения реализуются в параллельно-последовательной структуре устройства. Все соотношения решаются параллельно. Каждое соотношение решается последовательно за и тактов в каждой итерации.

Так как система базисных функций, сходящаяся последовательность угловых приращений arth 2 -/ не удовлетворяет условиям агй 2 < " art!> 2 !!=j!- то для устранения зон песходимости необходимое повторение по два раза только 4, 13-й и т. д. итераций, определяемых по формуле

j=3и+1,и=1,2,3,....

Это позволяет значительно сократить время вычислений.

Предмет изобретения

Устройство для вычисления обратного гиперболического тангенса,. содержащее три накопительных сдвигающих регистра, три сумматора-вычитателя, блок псевдочастного и блок управления, причем выходы младших триггеров первого, второго и третьего накопительных сдвигающих регистров соединены соответственно с первыми входами первого, второго и третьего сумматоров-вычитателей, выходы которых соединены со счетными входами старших триггеров соответствующих накопительных сдвигающих регистров; выход стар4

В л!обой итерации с блока управления выдается серия сдвигающих импульсов. Из содержания регистра 4 в сумматоре-вычитателе 1 вычитается сдвинутое в сторону младших разрядов переадресованное значение рс5 гистра i. По знаку разности определяется очередная цифра псевдочастного в блоке 10 (оператора поворота) — !/j, которая используется в следующей итерации. В сумматоревычитателе 2 происходит вычитание из содержания регистра 7 сдвинутого переадресованного значения регистра 4, т. е. перекрест»ое вычитание или сложение. В сумма!горевычитателе 3 осуществляется суммирование констант, поступающих из памяти, с предыдущим значением регистра 9. При очередной цифре q = — 1 происходит перемена опепаций в сумматорах-вычитателях.

После выполнения и итераций в регист® ре 4 содержимое его становится равным нулю. В регистре 7 содержание равно гиперболическому секa»cy, значение которого увеличено в /г„раз. В регистре 9 находится значение обратного гиперболического тангенса.

Для подавляющего большинства значений аргумента процесс сходится на итерации, номер которон j < n. При этом в регистре 9 находится точное значение обратного гиперболического тангенса, а в регистре 4 содержание равно нулю. Блок сравнения выдает сигнал сброса, когда все разряды регистра 4, кроме знакового, незначащие. Блок управления по этому сигналу прекращает подачу сдвигающих тактовых импульсов на следующей итерации. Этим обеспечивастся асинхронный ре>ким. Кроме того, блок управления при переходе к 5,. 14-й и т, д. итерациям не изменяет номер следующей итерации, поэтому в процессе участвуют прежние переадресованные составляющие, сдвинутые на то же число разрядов, и предыдущая: константа. 3!! !а!ение цифры псевдочастного д может быть различно на двух повторяемых итерациях, Для практически необходимой точности

45 при решениях задач. управления время цикла. вычисления обратного гиперболического тангснса в тактах равно Т < n + 5и + 4, что в два раза меньше, чем у протипа. Кроме того, одновременно получается значение гиперболического секанса.

465630

Составитель В. Тюрин

Техред Т. Миронова

Редактор И. Грузова

Корректор Н. Аук

".1аказ 4900 Изд. № 1328 Тираж 679

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, jK-35, Раушская наб., д. 4/5

Подписное

М0Т, Загорский филиал

mего триггера первого накопительного сдвигающего регистра соединен с входом блока псевдочастного, выход которого соединен с входами управления сумматоров-вычитателей; первые три выхода блока управления соединены со сдвигающими входами соответствующих накопительных сдвигающих регистров, отличающееся тем, что, с целью увеличения быстродействия и упрощения устройства, оно содержит два сдвигающих регистра, блок памяти и блок сравнения, причем информационные входы блока сравнения соединены с соответствующими выходами первого накопительного сдвигающего регистра, à его вы6 ход соединен с входом блока управления; четвертый и пятый выходы блока управления соединены соответственно со сдвигающими входами первого и второго сдвигающих реги5 стров, информационные входы которых соединены с одноименными информационными выходами соответственно первого и второго накопительных сдвигающих регистров, а выходы младших триггеров — с вторыми входами

10 соответственно второго и первого сумматороввычитателеи; шестой выход блока управления соединен с входом блока памяти, выход которого соединен с вторым входом третьего сумматора-вычитателя.