Аналого-цифровой фильтр

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii) 4657I5, Союз Советских

Сокиалистнческих

Республик (61) Дополнительное к авт. свид.-ву (22) Заявлено 29.01.73 (21) 1878742/26-21 с присоединением заявки № (23) Приоритет

Опубликовано 30.03.75. Бюллетень № 12

Дата опубликования описания 26.06.75

,51) М. Кл. Н 031т 7/10

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (53) УДК 621.394.44:

:621.372 (088.8) (72) Автор изобретения

В. С. Гладкий

Морской гидрофизический институт АН Украинской ССР (71) Заявитель (54) АНАЛОГО-ЦИФРОВОЙ ФИЛЬТР

Изобретение относится к области вычислительной техники и может использоваться при селективной обработке данных, представленных как в цифровой, так и в аналоговой форме, а также при статистической обработке данных, в измерительных системах для изменения или компенсации частотных свойств системы, Известно устройство, состоящее из блоков памяти, содержащих схемы выборки, преобразователей «аналог — код» и «код — аналог», блоков вероятностного округления, блоков матричного умножения, сумматоров, блока динамической памяти и блока управления.

В основу работы известного устройства положены аналоговые способы выполнения арифметических операций, в результате чего резко сужается частотный диапазон обрабатываемых сигналов.

Цель изобретения — увеличение быстродействия и диапазона частот входного сигнала, Это достигается тем, что в предлагаемом аналого-цифровом фильтре сигнал поступае r через преобразователь «аналог — код» или непосредственно на один из входов первого сумматора, другой вход которого подключен к выходу первого блока матричного умножения, одним из входов через первый блок вероятностного округления соединенного с блоком памяти, другим через второй блок вероятностного округления — с выходом блока динамической памяти, а непосредственно — с одним из входов второго блока матричного умножения, другие входы которого через третий блок

5 вероятностного округления соединены с выходом блока памяти и непосредственно с выходом первого сумматора, который подключен к входу блока динамической памяти, при этом выход второго блока матричного умно10 жения соединен с преобразователем «код— аналог» через второй сумматор.

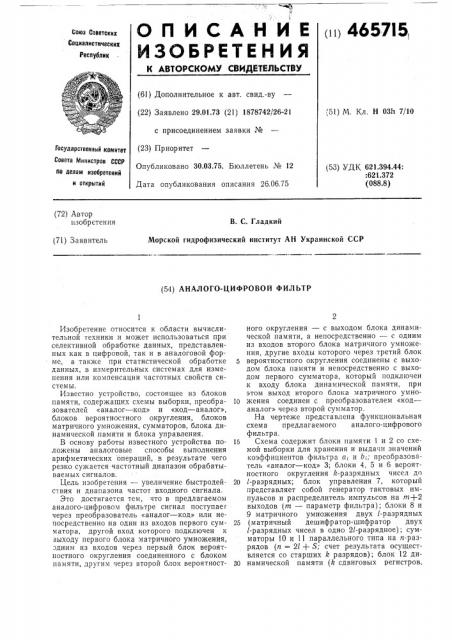

На чертеже представлена функциональная схема предлагаемого аналого-цифрового фильтра.

15 Схема содержит блоки памяти 1 и 2 со схемой выборки для хранения и выдачи значений коэффициентов фильтра а; и b;; преобразователь «аналог — код» 3; блоки 4, 5 и 6 вероятностного округления k-разрядных чисел до

20 l-разрядных; блок управления 7, который представляет собой генератор тактовых импульсов и распределитель импульсов на т,+2 выходов (m — параметр фильтра); блоки 8 и

9 матричного умножения двух l-разрядных

25 (матричный дешифратор-шифратор двух

E-разрядных чисел в одно 2l-разрядное); сумматоры 10 и 11 параллельного типа на и-разрядов (и = 2l+ S; счет результата осуществляется со старших k разрядов); блок 12 ди30 намической памяти (k сдвиговых регистров, 465715

Предмет изобретения

Х(л) Составитель М. Аудринг

Редактор E. Караулова Техред Т. Курилко Корректоры: А. Степанова и Л. Котова

Заказ 1394/7 Изд. № 1312 Тираж 902 Подписное

1 НИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )К-35, Раушская наб., д. 4!5

Типография, пр. Сапунова, 2 каждый на m разрядов); преобразователь

«код †анал» 13.

Аналого-цифровой фильтр работает следующим образом.

На вход Х®, если сигнал аналоговый, или

Х(п), если сигнал цифровой, подается очередное значение входного сигнала. При этом он суммируется в сумматоре 10 параллельного типа с ранее имевшимся в нем числом. Результат поступает в первые ячейки блока 12 динамической памяти и одновременно в блок 9 матричного умножения, где умножается с нулевым коэффициентом, взятым из блока памяти 2 и округленным в блоке 6 вероятностного округления. Затем начинается циклическое продвижение информации в блоке 12 динамической памяти, при котором на умножение в блоки 8 и 9 матричного умножения (после округления) последовательно поступают все числа, хранящиеся в блоке 12 динамической памяти. Последнее число переходит в т-ю ячейку, а первая ячейка остается незаполненной. Указанные числа умножаются одновременно на коэффициенты b; (результат заносится в сумматор 10) и на коэффициенты а; (результат заносится в сумматор 11). После окончания процедуры умножения и суммирования из сумматора 11 считывается очередное выходное значение уже отфильтрованного сигнала либо в цифровой форме Y(n), либо в аналоговой У®.

Если взять коэффициенты b„. равными нулю, то устройство выполняет функции нерекурсивного фильтра. При использовании элементов

4 с верхней частотой переключения, равной f, скорость подачи сигналов F на вход устройства равна = f/т.

Аналого-цифровой фильтр, состоящий из блоков памяти, содержащих схемы выборки, преобразователей «аналог — код» и «код — аналог», блоков вероятностного округления, блоков матричного умножения, сумматоров, блока динамической памяти и блока управления, отл и ч а ющи йся тем, что, с целью увеличения быстродействия и диапазона частот входного сигнала, сигнал поступает через преобразователь «аналог — код» или непосредственно на один из входов первого сумматора, другой вход которого подключен к выходу

20 первого блока матричного умножения, одним из входов через первый блок вероятностного округления соединенного с блоком памяти, другим через второй блок вероятностного округления — с выходом блока динамической

25 памяти, а непосредственно — с одним из входов второго блока матричного умножения, другие входы которого через третий блок вероятностного округления соединены с выходом блока памяти и непосредственно с выходом

30 первого сумматора, который подключен к входу блока динамической памяти, при этом выход второго блока матричного умножения соединен с преобразователем «код — аналог» через второй сумматор.