Устройство для сравнения двоичных чисел

Иллюстрации

Показать всеРеферат

ОПИСАН И Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и1 466508

Сове Сооетскик

СОЦИОЛИРТИЧОРКИК

Росиуолик (61) дополнительное к авт. свил-ву (22) Заявлено 06.02.73 (21) 1883472/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 05.04.75. Бюллетень № 13

Дата опубликования описания 16.07.75 (51) М. Кл. G 06f 7/04

Государственный комитет

Совета Министров СССР (53) УДК 681.332.65 (088.8) по дедам изосретеииЙ

И ОТКРЫТИЙ (72) Автор изобретения

М. А. Дуда (71) Заяв|пел (54) УСТРОЙСТВО ДЛЯ СРАВНЕНБЯ ДВО14ЧНЫХ ЧИСЕЛ

Изобретение относится к области автоматики и вычислительной техники, в частности к цифровым системам контроля и обработки информацииии.

Устройства для сравнения двоичных чисел, содержащие первый регистр, вход сложения которого подключен к входной шине устройства, а выходы разрядов соединены со входами соответствующих разрядов второго регистра через первую группу схем «И», другие входы которых соединены через первую схему

«ИЛИ», и элемент задержки с выходом второй схемы «И», соединенной через вторую схему

«ИЛИ» с шиной сброса второго регистра, а шина управления устройством соединена со входом сброса первого триггера и через третью схему «ИЛИ», другой вход которой через второй элемент задержки связан с шиной сброса устройства, с шинами сброса первого регистра и второго триггера и с другим входом второй схемы «ИЛИ», триггеры, схемы

«И», «ИЛИ» сравнения.

Однако такие устройства содержат большое число регистров, что снижает надежность работы, так как для получения наибольшего или наименьшего из следующих одно за другим чисел необходимо два отдельных устройства, выполняющих соответственные функции.

Целью изобретения является упрощение устройства.

Для этого в предлагаемом устройстве шина сброса соединена с одним из входов третьей схемы «И», другой вход которой подключен к инверсному выходу первого триггера, а вы5 ход — к другому входу первой схемы «ИЛИ», со входом второй схемы «И», другой вход которой через четвертую схему «ИЛИ» подключен к выходу пятой и четвертой схем «И», одни из входов которых соединены с шинами вы1о борки наименьшего и наибольшего из чисел, а другие с прямым и инверсным выходами второго триггера соответственно. Вход установки в единичное состояние второго триггера подключен к выходу схемы сравнения, входы

15 которой связаны с выходами разрядов обоих регистров.

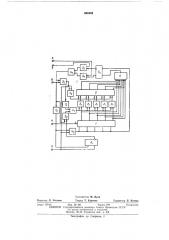

Блок-схема устройства представлена на чертеже.

Устройство содержит регистры 1, 2, схемы

2О «И» 3 — 33, схемы «ИЛИ» 4i — 44, схему сравнения 5, триггеры бь 63,элементы задержки 71, 72 и входные шины 8 — 12.

Устройство работает следующим образом.

Сигнал установки исходного состояния уст25 ройства, поступающий на входную шину 12, устанавливает регистры 1, 2 и триггеры бь 63 в нулевое состояние.

Первое число, поступающее на вход 11, записывается в регистр 1, а сигнал сброса, по.

30 ступающий после первого числа на входную

466508

15

20 шину 10, через схему «И» Зз, управляемую нулевым выходом триггера 6ь и схему «ИЛИ»

4ь переписывает это двоичное число в регистр 2. При этом триггер 6> и регистр 1 сигналом сброса через линию задержки 7 устанавливаются в единичное и исходное состояния соответственно. Второе число, поступающее на вход 11, также записывается в регистре 1.

Если второе двоичное число окажется больше или равно первому двоичному числу, записанному в регистре 2, то на выходе схемы сравнения двух кодов 5 в момент равенства чисел в регистрах 1 и 2 появляется сигнал, который перебрасывает триггер 6> в единичное состояние. Поступающий после числа на входную шину 10 сигнал сброса через схемы «И»

3 и «ИЛИ» 4> устанавливает регистр 2 в исходное состояние, а через линию задержки 7> и «ИЛИ» 4> перезаписывает двоичное число, находящееся в регистре 1, в регистр 2, если разрешающий потенциал на шинах выборки наибольшего 8 или наименьшего 9 из следующих одно за другим чисел и триггер 6 — в единичном или нулевом состоянии соответственно и не перезаписывает двоичное число, находящееся в регистре 1, в регистр 2, если триггер 6,— в нулевом или единичном состоянии соответственно.

При этом триггер 6 и регистр 1 сигналом сброса через линию задержки 7> и схему

«ИЛИ» 4З устанавливаются в исходном состоянии.

При поступлении на вход устройства следующего сравниваемого числа операция сравнения производится аналогично описанному, и результат сравнения всегда оказывается записанным в регистре 2.

Если, например, на вход 11 устройства поступают следующие одно за другим числа, заданные последовательностями импульсов, и разрешающий потенциал на шине выборки наименьшего 9 из следующих одно за другим чисел, то сигнал сброса, поступающий после первого числа через схемы «И» 3 и «ИЛИ» 4ь переписывает первое двоичное число из регистра 1 в регистр 2, и дальнейшая перезапись двоичных чисел из регистра 1 в регистр 2 происходит только тогда, когда триггер 6 в нулевом состоянии и сигналы сброса поступают после соответствующих чисел через схему «И»

3>, линию задержки 7> и схему «ИЛИ» 4ь

В результате в регистре 2 будет наименьшее из следующих одно за другим чисел, заданных последовательностями импульсов.

Если на вход устройства 11 поступают следующие одно за другим числа, заданные последовательностями импульсов, и разрешающий потенциал на шине выборки наибольшего

8 из следующих одно за другим чисел, то сигнал сброса, поступающий после первого числа через схемы «И» 3> и «ИЛИ» 40 переписывает первое двоичное число из регистра 1 в регистр 2, и дальнейшая перезапись других чисел из регистра 1 в регистр 2 происходит только тогда, когда триггер 6 — в единичном состоянии и сигналы сброса поступают после соответствующих чисел через схему «И» 3, линию задержки 7> и схему «ИЛИ» 4ь

В результате в регистре 2 будет наибольшее из следующих одно за другим чисел, заданных последовательностями импульсов.

Предмет изобретения

Устройство для сравнения двоичных чисел, содержащее первый регистр, вход сложения которого подключен к входной шине устройства, а выходы разрядов соединены со входами соответствующих разрядов второго регистра через первую группу схем «И», другие входы которых соединены через первую схему «ИЛИ» и элемент задержки с выходом второй схемы

«И», соединенной через вторую схему «ИЛИ» с шиной сброса второго регистра, а шина управления устройством соединена со входом сброса первого триггера и через третью схему

«ИЛИ», другой вход которой через второй элемент задержки связан с шиной сброса устройства, с шинами сброса первого регистра и второго триггера и с другим входом второй схемы

«ИЛИ», триггеры, схемы «И», «ИЛИ» и сравнения, отличающееся тем, что, с целью упрощения устройства, в нем шина сброса соединена с одним из входов третьей схемы «И», другой вход которой подключен к инверсному выходу первого триггера, а выход — к другому входу первой схемы «ИЛИ», со входом второй схемы «И», другой вход которой через четвертую схему «ИЛИ» подключен к выходу пятой и четвертой схем «И», одни из входов которых соединены с шинами выборки наименьшего и наибольшего из чисел, а другие— с прямым и инверсным выходами второго триггера соответственно; вход установки в единичное состояние второго триггера подключен к выходу схемы сравнения, входы которой связаны с выходами разрядов обоих регистров.

466508

Составитель М. Дуда

Техред Т. Курилко

Редактор Л. Утехина

Корректор Л. Котова

Типография, пр. Сапунова, 2

Заказ 1974)2 Изд. № 641 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, Ж-35, Раушская наб., д. 4/5