Интегратор напряжения

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ш 467361

Союз Советских

Социалистических

Республик (G1) Зависимое от авт. свидетельства (22) Заявлено 12.10.73 (21) 1964771/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 15.04.75. Бюллетень № 14

Дата опубликования описания 23.07.75 (51) М. Кл. G 06K 7/18

Государственный комитет

Совета Министров СССР ао делам изобретений и открытий (53) УДК 681.335.7 (088.8) (72) Авторы изобретения

В. А. Засенко, В. Г. Ивкин, И. В. Мозин и Е. Е. Трифонов (71) Заявитель (54) И НТЕГРАТОР НАП РЯЖЕНИЯ

Изобретение относится к измерительной технике.

Известны интеграторы напряжения, предназначенные для исследования физических процессов и основанные на методе двухтактного интегрирования. Они содержат последовательно соединенные интегрирующий усилитель и сравнивающее устройство, ключи, через первый ключ вход интегратора соединен со входом интегрирующего усилителя, вход последнего соединен через второй и третий ключи с источниками эталонных напряжений, схемы совпадсния, схему измерения времени, триггер управления, единич|ный выход которого подключен к управляющему входу первого ключа.

Для поддержания таких устройств в состоянии готовности к интегрированию в любой момент времени используются ключи, шунтирующие интегрирующий конденсатор и вход усилителя.

Существенным недостатком таких интеграторов является зависимость выходного результата от величины и стабильности порога срабатывания сравнивающего устройства.

Известные методы уменьшения влияния дрейфа и величины порога срабатывания сравнивающего устройства на точность, используе-мые в интегрирующих преобразователях цифровых вольтметров, не позволяют синхронизировать момент начала интегрирования с началом физического процесса.

С целью повышения точности, в предложенном интеграторе вход первой схемы совпадения соединен непосредственно с выходом сравнивающего устройства, вход второй схемы совпадения — через инвертор, разрешающие входы схем совпадения подключены к нулевому выходу триггера, а выходы подключены

10 к управляющим входам второго и третьего ключей.

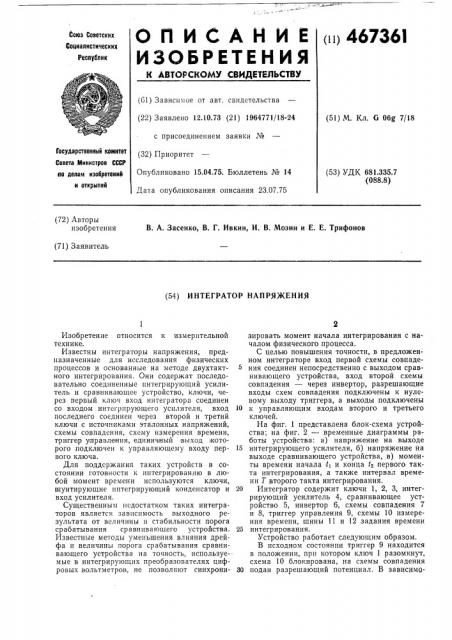

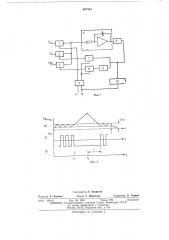

На фиг. 1 представлена блок-схема устройства; на фиг. 2 — временные диаграммы работы устройства: а) напряжение на выходе

15 интегрирующего усилителя, б) напряжение на выходе сравнивающего устройства, в) моменты времени начала 4 и конца 4 первого такта интегрирования, а также интервал времени Т второго такта интегрирования.

20 Интегратор содержит ключи 1, 2, 3, интегрирующий усилитель 4, сравнивающее устройство 5, инвертор 6, схемы совпадения 7 и 8, триггер управления 9, схемы 10 измерения времени, шины 1l и 12 задания времени

25 интегрирования.

Устройство работает следующим образом.

В исходном состоянии триггер 9 находится в положении, прп котором ключ 1 разомкнут, схема 10 блокирована, на схемы совпадения

30 подан разрешающий потенциал. В зависимо467361

55 сти от полярности напряжения на выходе сравнивающего устройства U„„разрешающий потенциал подается через схему совпадения

7 или 8 на управляющий вход ключа 2 или 3 соответственно. На вход интегрирующего усилителя подключается источник эталонного напряжения той полярности, интегрирование напряжения которого приводит к срабатыванию сравнивающего устройства и изменению полярности напряжения UÄ. Например, под воздействием напряжения дрейфа положительной полярности на входе интегрирующего усилителя напряжение на его выходе U,„,„ достигает нижнего порога срабатывания сравни вающето устройства U H, на выходе последнего появляется напряжение положительной полярности, при которой ко входу интегрирующего усилителя через ключ 2 подключается источник отрицательного эталонного напряжения (— U,). Это вызывает изменение выходного напряжения интегратора в направлении, противоположном предыдущему. Напряжение U„,, „достигает верхнего порога срабатывания сравнивающего устройства UÄ.

Выходное напряжение сравнивающего устройства U„, изменяет свою полярность, становится отрицательным, в результате чего ключ 2 закрывается, а ключ 3 открывается. Интегрирование напряжения + U; приводит к уменьшению Ua r Ä Это пилообразное напряжение достигает уровня UÄÄ, срабатывает сравнивающее устройство, вновь напряжение

U, становится положительным. Далее картина повторяется.

В момент времени 4 на шину 11 поступает импульс начала интегрирования физического процесса и устанавливает триггер 9 в положение, при котором замыкается ключ 1, блокируются схемы совпадения 7 и 8, размыкаются ключи 2 и 3. В течение времени первого такта интегрируется напряжение U„„, приложенное ко входу устройства.

В момент времени t> на шину 12 поступает импульс окончания интегрирования физического процесса и устанавливает триггер 9 в исходное состояние. Начинается второй такт.

Ключ 1 закрывается, включается схема 10 измерения времени второго .такта, на схемы совпадения 7 и 8 подается разрешающий потенциал. Замыкается один из ключей 2 или 3, автоматически подключая на вход интегрирующего усилителя эталонное напряжение полярности, противоположной полярности входного напряжения.

Интегрирование выбранного напряжения

Зо

35 продолжается в течение второго такта до момента срабатывания сравнивающего устройства. В указанный момент вновь блокируется схема 10 измерения времени, результат, записанный в ней, пропорционален интегралу входного напряжения за время первого такта.

С этого же момента вновь начинается процесс компенсации дрейфа интегрирующего усилителя.

В паузе между измерениями напряжение на выходе интегрирующего усилителя поддерживается на уровне порога срабатывания сравнивающего устройства с точностью, определяемой разностью его верхнего и нижнего уровней (чувствительностью) . Эту разность легко свести к минимуму путем использования в качестве сравнивающего устройства усилителя с большим коэффициентом усиления. Таким о бр азом, устройство всегда готово к интепрированию физического процесса и обеспечивает высокую точность результата, так как напряжения на выходе интегрирующего усилителя в начале первого такта и в конце второго такта совпадают.

В предложенном интеграторе исключается погрешность результата, обусловленная величиной и нестабильностью порога срабатывания сравнивающего устройства. В то же время положительные качества известных устройств сохранены.

Интегратор может найти применение в различных областях измерительной техники, например для измерения магнитных полей в кольцевых ускорителях заряженных частиц.

Предмет изобретения

Интегратор напряжения, содержащий последовательно соединенные интегрирующий усилитель и сравнивающее устройство, ключи, через первый ключ вход интегрирующего усилителя соединен со входом устройства, а через второй и третий ключи — с источниками эталонных напряжений, схемы совпадения, схему измерения времени, триггер управления, единичный выход которого подключен к управляющему входу первого ключа, отличающийся тем, что, с целью повыШения точности, вход первой схемы совпадения соединен непосредственно с выходом сравнивающего устройства, вход второй схемы совпадения — через инвертор, разрешающие входы схем совпадения подключены к нулевому выходу триггера, а выходы подключены к управляющим входам второго и третьего ключей, Фиг.1 а) Составитель Е. Трифонов

Техред Т. Миронова

Редактор Б. Нанкина

Корректор О. Тюрина

Заказ

Типография, пр. Сапунова, 2

1654 6 Изд. № 1365 Тираж 679 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )Ê-35, Раушская наб., д. 415