Многостабильная ячейка памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОЬРЕтЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ и)) 46740 5

Союз Советских

Социалистических

Республик (61) Зависимое от авт. свидетельства (22) Заявлено 16.02.73 (21) 1884318/18-24 с присоединением заявки № (32) Приоритет

Опубликовано 15.04.75. Бюллетень № 14 (51) М. Кл. G 1lс 11/34

G l l c 11!38

Государственный комитет

Совета Мынистрав СССР (53) УДК 628.327.6 (088,8) по делам изобретений и открвпий

Дата опубликования описания 18.07.75 (72) Автор изобретения

Э. И. Багдасарьянц (71) Заявитель (54) МНОГОСТАБИДЬНАЯ ЯЧЕЙКА ПАМЯТИ

Изобретение относится к области импульсной схемотехники, а именно к импульсным схемам на тиристорах и на многостабильных элементах. Оно может найти широкое применение в вычислительной технике, в частности в пересчетных устройствах, в системах автоматического управления и прочее.

Известны тиристорные переключатели с многостабильной характеристикой, построенные на основе структур типа р-п-р-п.

Цель изобретения заключается в создании многостабильной тиристорной ячейки памяти со стабилизированным значением тока переключения из дополнительного открытого состояния в основное открытое состояние.

Эта цель достигается тем, что предлагаемая многостабильная ячейка памяти содержит дополнительный управляющий транзистор и туннельный диод, анод которого соединен с эмиттером тетристора и коллектором дополнительного управляющего транзистора, а катод туннельного диода и эмиттеры управляющих транзисторов соединены с шиной нулевого потенциала.

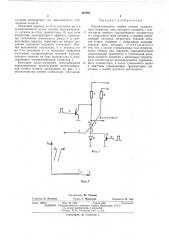

На фиг. l приведена схема описываемой ячейки памяти.

Многостабильная ячейка памяти содержит четырехвыводной тетристор 1, имеющий вывод 2 к базовой области р-типа проводимости, первый управляющий электрод 3 тетристора

2 базовой области и-типа проводимости, анод 4 тетристора и катод 5, управляющий транзистор 6, резистор 7, включенный в анодную цепь тетристора, резистор 8, подключенный к

5 выводу 3. Катод 5 подсоединен к аноду туннельного диода 9. Дополнительный управляющий транзистор 10 соединен коллектором с анодом туннельного диода 9, шунтируя последний, а эмиттером — с шиной нулевого по10 тенциала. Позицией 11 обозначен базовый вывод транзистора 6, поз. 12 — базовый вывод транзистора 10.

Схема многостабильной ячейки памяти работает следующим образом (рассмотрение

15 проводится для случая трех стабильных состояний).

Включение тетристора во второе состояние (основное открытое состояние) осуществляет20 ся подачей положительного сигнала на первый управляющий электрод. Дальнейшее увеличение тока 1 через открытый тетристор l не изменяет его состояния, пока величина I остается меньше значения тока переключения Iuep.

25 Когда ток через открытый тетристор l достигает значения I,р, происходит выключение туннельного диода 9 и переход тетристора 1 во второе открытое состояние (3-е стабильное состояние), которое отличается по напряже30 нию от предыдущего состояния на величину

467405

Предмет изобретения

Фиг,2

Составитель Ю. Ушаков

Техред Т. Миронова

Корректор Н. Аук

Гедактор Б. Наикина

Заказ 1665/4 Изд. № 1394 Тираж 648 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

Москва, )K-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2 падения напряжения на выключенном туннельном диоде 9.

Обратный переход из 3-го состояния во "-е осуществляется путем подачи положительного сигнала на базу транзистора 10; при этом вследствие шунтирующего эффекта происходит включение туннельного диода 9 и соответственно переход тиристора во второе состояние (основное открытое ссстояние). Полное выключение тетристора, т, е. перевод его из 2-го состояния в 1-е состояние (закрытое состояние) осуществляется подачей положительного сигнала на базу транзистора 6, шунтирующего четырехвыводной тетристор 1.

Выходная вольт-амперная трехстабильная характеристика предлагаемой многостабильной ячейки памяти изображена на фиг. 2 с обозначениями ветвей стабильных состояний.

Многостабильная ячейка памяти, содержащая тетристор, анод которого соединен с коллектором первого управляющего транзистора и с резистором цепи питания, а первый управляющий электрод тетристора базовой области и-типа соединен с резистором дополнительной цепи питания, отличающаяся

10 тем, что, с целью стабилизации тока переключения ячейки, она содержит дополнительный управляющий транзистор и туннельный диод, анод которого соединен с эмиттером тетристора и коллектором дополнительного управляю15 щего транзистора, а катод туннельного диода и эмиттеры управляющих транзисторов соединены с шиной нулевого потенциала.